Configuration and Installation

Chapter 2

SCXI-1100 User Manual

2-28

© National Instruments Corporation

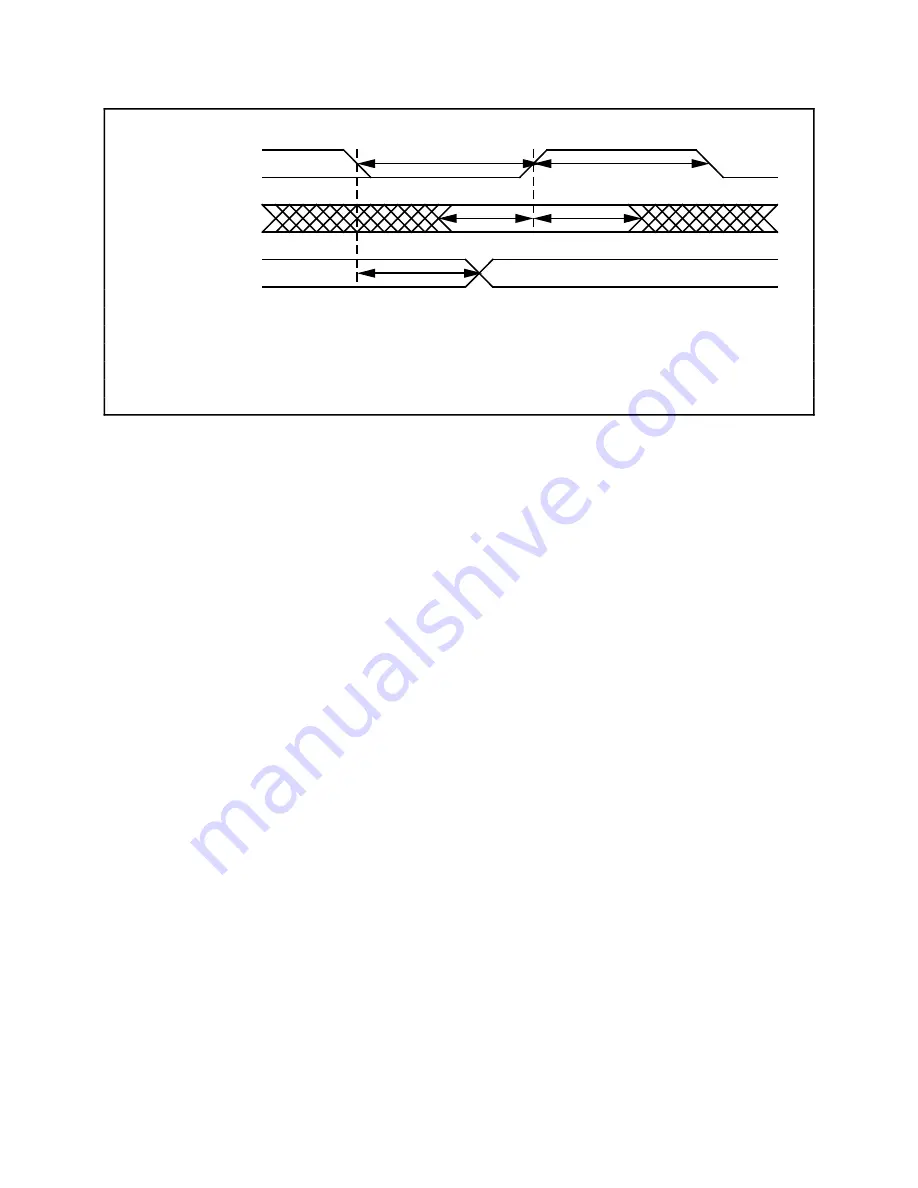

T

low

T

high

SERCLK

SERDATIN

SERDATOUT

T

setup

T

hold

T

delay

T

low

Minimum low time

65 nsec minimum

T

high

Minimum high time

400 nsec minimum

T

setup

SERDATIN setup time

200 nsec minimum

T

hold

SERDATIN hold time

200 nsec minimum

T

delay

SERDATOUT delay

350 nsec maximum

Figure 2-11. Serial Data Timing Diagram

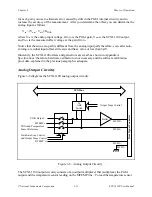

After the Slot-Select line to an SCXI-1100 has been asserted, you can write to the module

Configuration Register and read from the Module ID Register using the following protocols.

Deassert Slot-Select to reinitialize the contents of the Module ID Register. After the 32 bits of

data are read from the Module ID Register, further data will be zeros until reinitialization occurs.

To write to the Configuration Register, perform the following steps:

1. Initial conditions:

SS* asserted low.

SERDATIN = don't care.

DAQD*/A = 0 (indicates data will be written to the Configuration Register).

SLOT0SEL* = 1.

SERCLK = 1 (and has not transitioned since SS* went low).

2. For each bit to be written:

Establish the desired SERDATIN level corresponding to this bit.

Clear SERCLK to 0.

Set SERCLK to 1. Clock the data.

3. Pull SLOT0SEL* low to deassert the SS* line and establish conditions for writing a new

slot-select number to the Slot 0 Slot-Select Register.

4. If you are not selecting another slot, write zero to the Slot 0 Slot-Select Register.

Figure 2-12 illustrates a write to the SCXI-1100 Configuration Register of the binary pattern:

00010010 10011111 00000111