PRELIMINARY ISD1700 SERIES

Publication Release Date: Nov 6, 2008

- 41 -

Revision 1.31

Before starting to write the program code, one has to fully understand the definition of each command

and how to implement each of them correctly. If not, you may end up to spend lots of time and efforts

in debugging the program code. The following several sections illustrate exactly how the

communication sequence of each SPI command should be. Bear in mind that the first bit of each input

data byte shifting into the MOSI must be LSB, whereas the first bit of data byte coming out from the

MISO is LSB. Also, care must be provided to fulfill the initial conditions on the

SS

, SCLK and MOSI

inputs (as shown in Section 10.2). If wrong format is sent, then the device may not response at all or

may respond strangely. Also, not every command will generate an interrupt feedback signal to the

host in responding to the operation requested. Thus, precautions must be well considered to ensure

that the device is ready to accept a new instruction. Otherwise, the instruction sent will be ignored.

11.1 SPI

P

RIORITY

C

OMMANDS

This class of SPI commands will always be accepted by the ISD1700. They control power up and

down of the device, interrogating the status of the device and clearing interrupt requests.

11.1.1 PU (0x01) Power Up

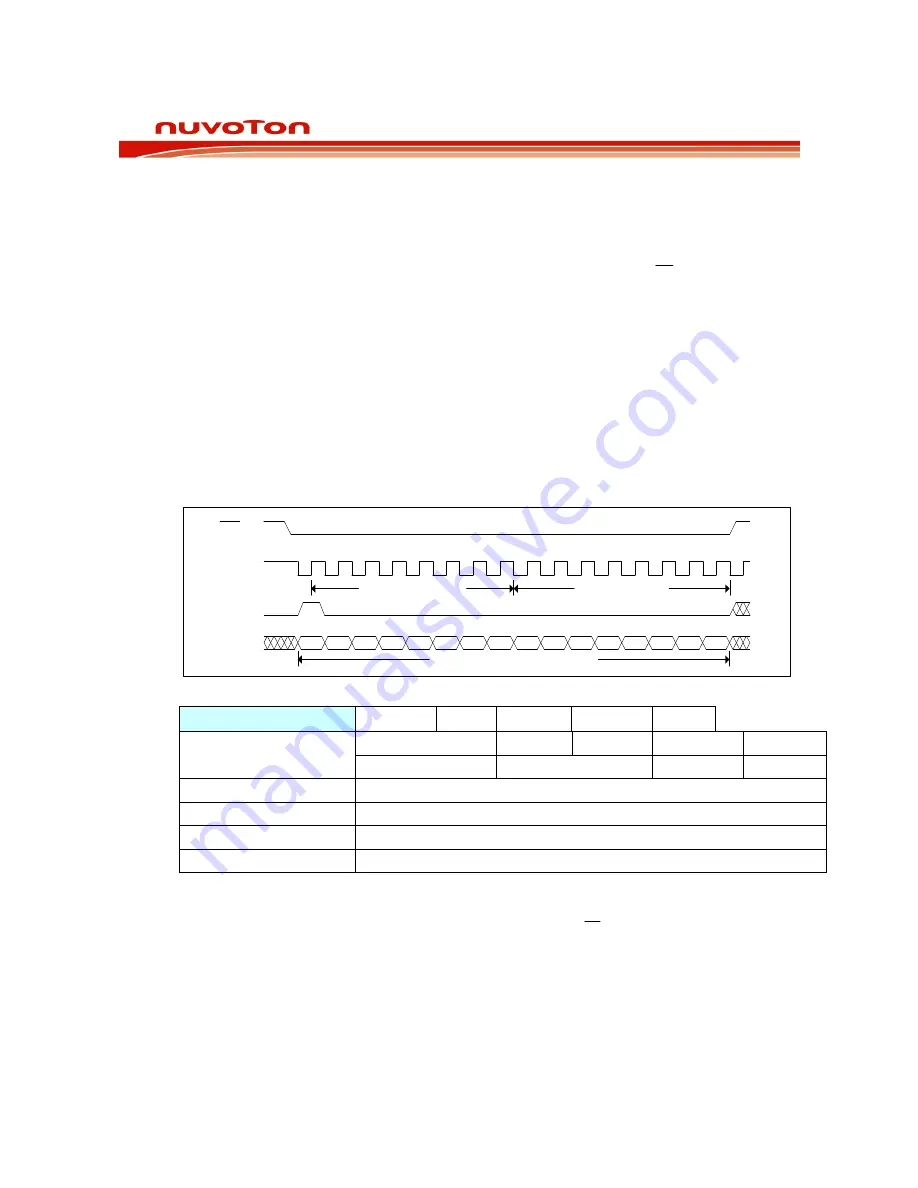

B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15

SCLK

MOSI

MISO

SS

Data Byte 1

Command (01h)

LSB

MSB

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

LSB

MSB

Status Register 0 : Bytes #1 & #2

PU

Opcode: 0x01 0x00

Interrupt: No

Byte Sequence:

MOSI

0x01

0x00

MISO SR0

Description: Power

up

State before Execution

Power Down

State after Execution

Idle/FT

Registers Affected

SR0: PU bit, SR1: RDY bit

This command wakes up the ISD1700 device and enables it into the idle state. Upon

executing this command, PU bit of SR0 and RDY bit of SR1 are set to 1. This command does

not generate an interrupt. Once in SPI mode, the input from

FT

pin is ignored and its function

is replaced by Bit 6 of the APC register. SPI mode is exited via a PD (power down)

command.