76

CMX32M cpuModule

BDM-610000075

Rev B

0x9FC: SGT_DATA

This register is used to view and modify the data in the Scatter-Gather Table. It is indexed both by

SELECT[CGT_Channel] (to select the channel), and SGT_ROW (to select the row in the table).

The Scatter-Gather Table consists of a list of up to 64 entries. Each entry contains the physical address of a buffer

that is 4kB in size, and 4kB aligned. It also contains a flag to indicate that the entry is valid. The Channel 1 Table

also includes flags to stop DMA transfers, restart the SGT, or generate and interrupt. These are flags that effect

all channels, and are only stored in the channel 1 table.

The DMA engine will transfer data using the same row of the SGT and the same offset for all channels. This

guarantees that the captured data is synchronized. The DMA engine will always iterate through the SGT, even if

DMA is not enabled for any channels.

The Scatter-Gather Table is not cleared at power up or during reset. Therefore, software must assume that it

contains random, invalid data.

ADDRESS

: The upper 20-bits of a DMA buffer 4k in size and 4k aligned. The DMA data will start at an offset of

0 into the buffer. After it is full, the DMA engine will advance to the next row in the table based on the flags.

IRQ:

Flag to generate and interrupt after this buffer is full. The interrupt will be generated for all channels that

DMA is enabled on. This flag is only checked for Channel 1.

STOP:

Flag to stop DMA on all channels after this buffer is full. This flag is only checked for Channel 1.

RESTART:

Flag to restart the SGT at row 0 after this buffer is full. This flag should always be set for the last entry

in the table, even if the STOP flag is also set. This flag is only checked for Channel 1.

VALID:

Flag to indicate that this is a valid entry. DMA data will only be transferred if the VALID flag is set. This

flag is checked for all channels.

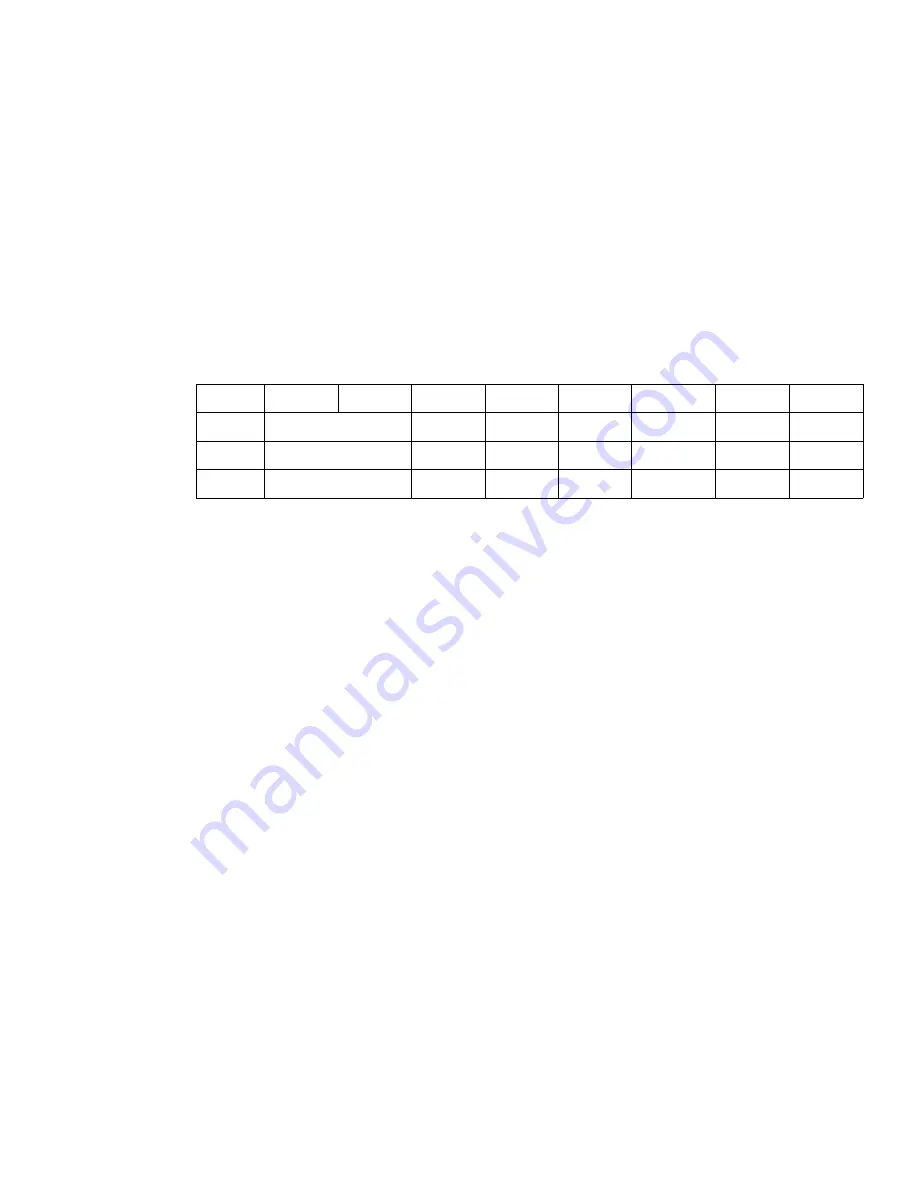

0x9FC: SGT_DATA

Register

Bit

31

12

11 9

8

7

6

5

4 0

Mode

R/W

R

R/W

R/W

R/W

R/W

R

Default

X

X

X

X

X

X

00000

Field

ADDRESS

Rsvd

IRQ

STOP

RESTART

VALID

Rsvd

Summary of Contents for BDM-610000075

Page 3: ... Accessing the Analog World www rtd com ISO9001 and AS9100 Certified CMX32M cpuModules ...

Page 4: ...iv CMX32M cpuModule BDM 610000075 Rev B ...

Page 30: ...22 CMX32M cpuModule BDM 610000075 Rev B ...

Page 60: ...52 CMX32M cpuModule BDM 610000075 Rev B ...

Page 102: ...94 CMX32M cpuModule BDM 610000075 Rev B ...

Page 116: ...108 CMX32M cpuModule BDM 610000075 Rev B ...