RTD Embedded Technologies, Inc.

| www.rtd.com

29

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

Voltage values for each bit will vary depending on input range and gain. For example, if the input is set for ±5, the formula for calculating

voltage is as follows:

𝑉𝑜𝑙𝑡𝑎𝑔𝑒 =

𝐼𝑛𝑝𝑢𝑡 𝑅𝑎𝑛𝑔𝑒

2

18

× 𝐶𝑜𝑛𝑣𝑒𝑟𝑠𝑖𝑜𝑛 𝐷𝑎𝑡𝑎

𝑉𝑜𝑙𝑡𝑎𝑔𝑒 =

10

2

18

× 𝐶𝑜𝑛𝑣𝑒𝑟𝑠𝑖𝑜𝑛 𝐷𝑎𝑡𝑎

𝑉𝑜𝑙𝑡𝑎𝑔𝑒 = 38.15µ𝑉 × 𝐶𝑜𝑛𝑣𝑒𝑟𝑠𝑖𝑜𝑛 𝐷𝑎𝑡𝑎

5.6.1

I

NITIALIZING THE

ADC

C

ONVERTER

The following is a list of the typical steps needed to initialize the ADC converter and begin sampling:

1.

Set the ADC to the Uninitialized state (MODE = Uninitialized)

2.

Setup the DMA for the channel

3.

Set the input mode (CH_FRONT_END_CONFIG)

4.

Set the start and stop triggers (START_TRIG, STOP_TRIG)

5.

Set the clock source (CLK_SOURCE)

6.

Set the sample rate (CLK_DIV_CNTR)

7.

Set the Pre and/or Post Capture counters (PRE_TRIGGER_CAPTURE, POST_STOP_CAPTURE)

8.

Set the ADC to the Reset state (MODE = Reset)

9.

Start the DMA

10.

Start the ADC (MODE = Go)

5.6.2

S

IMPLIFIED BLOCK DIAGRAM OF ANALOG INPUT

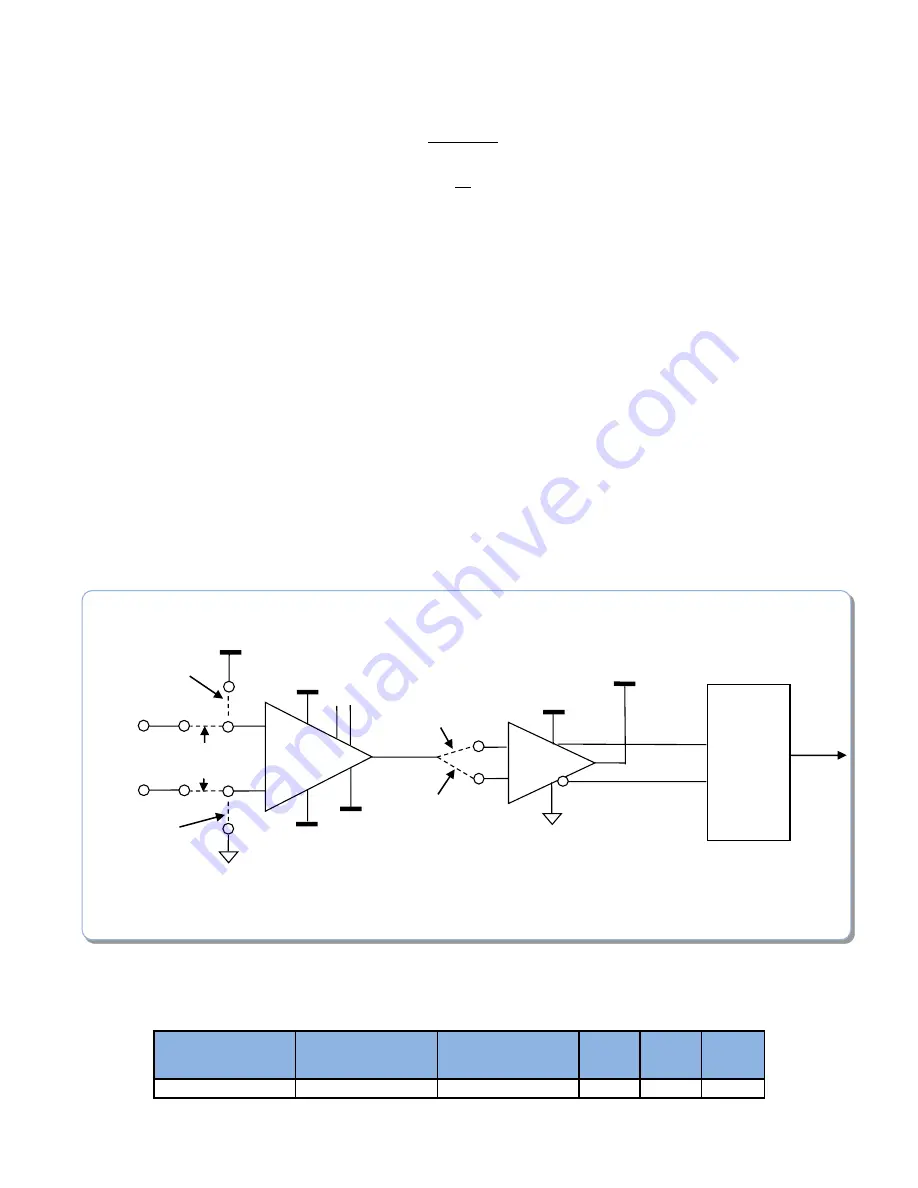

The following figure shows the front end circuit for the DM35418HR/DM35218HR. It also shows the names of the FPGA registers in bold and

the different ways the front-end can be configured for different modes of operation.

Figure 9: Analog Input Front End

Table 15: ADC Full-Scale Settings

CHn_Front_End_Config

[PGA_A1]

CHn_Front_End_Config

[PGA_A0]

CHn_Front_End_Config

[G_05_1]

Signal

Path

Gain

Unipolar

Mode

Bipolar

Mode

0

0

0

0.5

n/a

±10V

+

-

VREF

CHn_Front_End_Config

[PGA_A[1:0]]

G=1

:

0, 0

G=2 : 0, 1

G=4 : 1, 0

G=8 : 1, 1

+15V

-15V

CHn_Front_End_Config

[SE_DIFF]

A1 A0 -> G

Gain

CHn_Front_End_Config

[VREF_NORMAL]

CHn_Front_End_Config

[BIP_UNI]

VREF: 0V: [BIP_UNI] = 0

VREF: -5V: [BIP_UNI] = 1

SE_DIFF = 0

SE_DIFF =1

IN+

*

IN-

*

VREF_NORMAL = 0

VREF_NORMAL = 1

+5V

0.5V.. 4.5V

4.5V.. 0.5 V

2.5V common

0.5 V

*0.8

Precision attenuator

5V

VOCM

2.5V

05_1 = 0

*0.4

18bit 1.5MHz A/D - LTC2379

IN+

IN-

SDO

To FPGA

CHn_Front_End_Config

[G_05_1]

05_1= 1

*For of DIFF sources, a return path to board ground must be provided.