RTD Embedded Technologies, Inc.

| www.rtd.com

47

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

6.5.8

POST_STOP_CONVERSIONS

(R

EAD

/W

RITE

)

Number of conversions to send after the Stop Trigger.

6.5.9

CONVERSION_CNT

(R

EAD

O

NLY

)

Total number of conversions. It also continues counting after a Re-Arm.

6.5.10

INT_ENA

(M

ASKABLE

R

EAD

/W

RITE

)

Each bit corresponds to an interrupt source. A value of ‘1’ enables the source, and a value of ‘0’ disables it. See below for a description of the

sources.

6.5.11

INT_STAT

(R

EAD

/C

LEAR

)

Each bit corresponds to an interrupt source. Reading a value of ‘1’ indicates that an event has occurred. Reading a value of ‘0’ indicates that the

event has not occurred. Writing a ‘1’ will clear that bit.

B[0]: Conversion – A value has been sent.

B[1]: Channel Marker – One of the channels has an enabled marker.

B[2]: Reserved

B[3]: Start Trigger

B[4]: Stop Trigger

B[5]: Post-Stop Conversions Completed

6.5.12

CLK_SRC_GBL

N

NOTE: If a CLK_SRC_GBL is unassigned in all function blocks, it defaults to

System Clock/Immediate.

Selects the source to drive onto Clock Bus signal N.

B[7:0]:

o

0x00: Disable Clock Source

o

0x80: Conversion – A value has been sent.

o

0x81: Channel Marker – One of the channels has an enabled marker.

o

0x82: Reserved

o

0x83: Start Trigger

o

0x84: Stop Trigger

o

0x85: Post-Stop Conversions Completed

6.5.13

DA_CONFIG

(M

ASKABLE

R

EAD

/W

RITE

)

Not used.

6.5.14

CH_FRONT_END_CONFIG

(M

ASKABLE

R

EAD

/W

RITE

)

This register provides configuration to the Front End for this DAC Channel.

B[1:0]: PGA_A[1:0]

o

PGA_A[1:0]: 00: Gain of 1

o

PGA_A[1:0]: 01: Gain of 2

o

PGA_A[1:0]: 10: Gain of 4

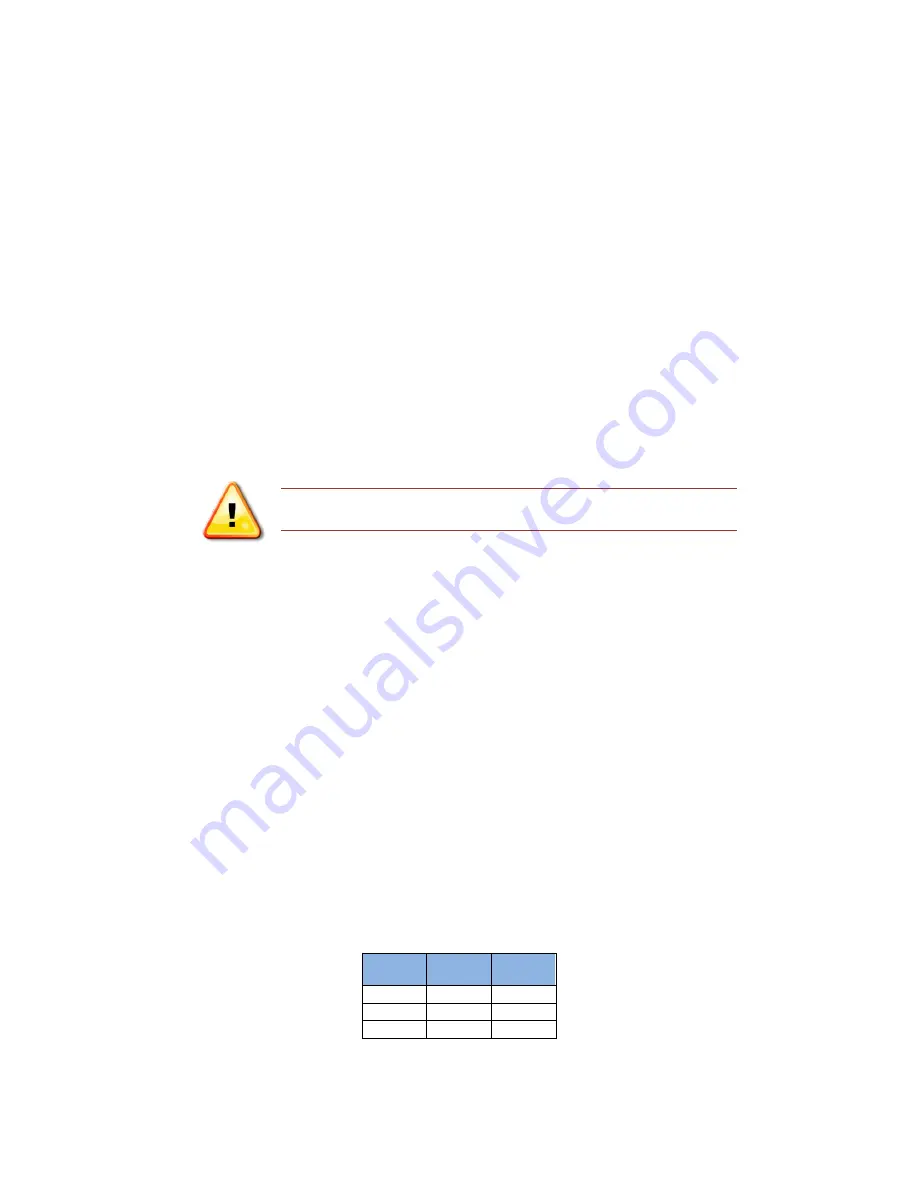

Table 24: DAC Full-Scale Settings

PGA_A[1

:0]

Gain

Range

00

1

±2.5V

01

2

±5V

10

4

±10V