3.5.5

Semaphore Operations

If two or more CPUs in one programmable controller (see Chapter 10)

require access to the same global memory area (peripherals, CPs, IPs),

there is a danger that one CPU will overwrite the data of another CPU

or that one CPU could read invalid intermediate data statuses of

another CPU and misinterpret them. You must therefore coordinate

CPU accesses to the common memory areas.

You can coordinate the individual CPUs using the SED and SEE

operations.

You can, for example, program the following coordination between two

CPUs: a CPU involved in multiprocessing can only access the common

memory area after it has successfully set a declared semaphore (SES). A

semaphore xx can only be set by a single CPU. If a CPU fails to set (i.e.

disable) the semaphore, it cannot access the memory area. In the same

way, a CPU can no longer access the memory once it has released the

semaphore again (SEE).

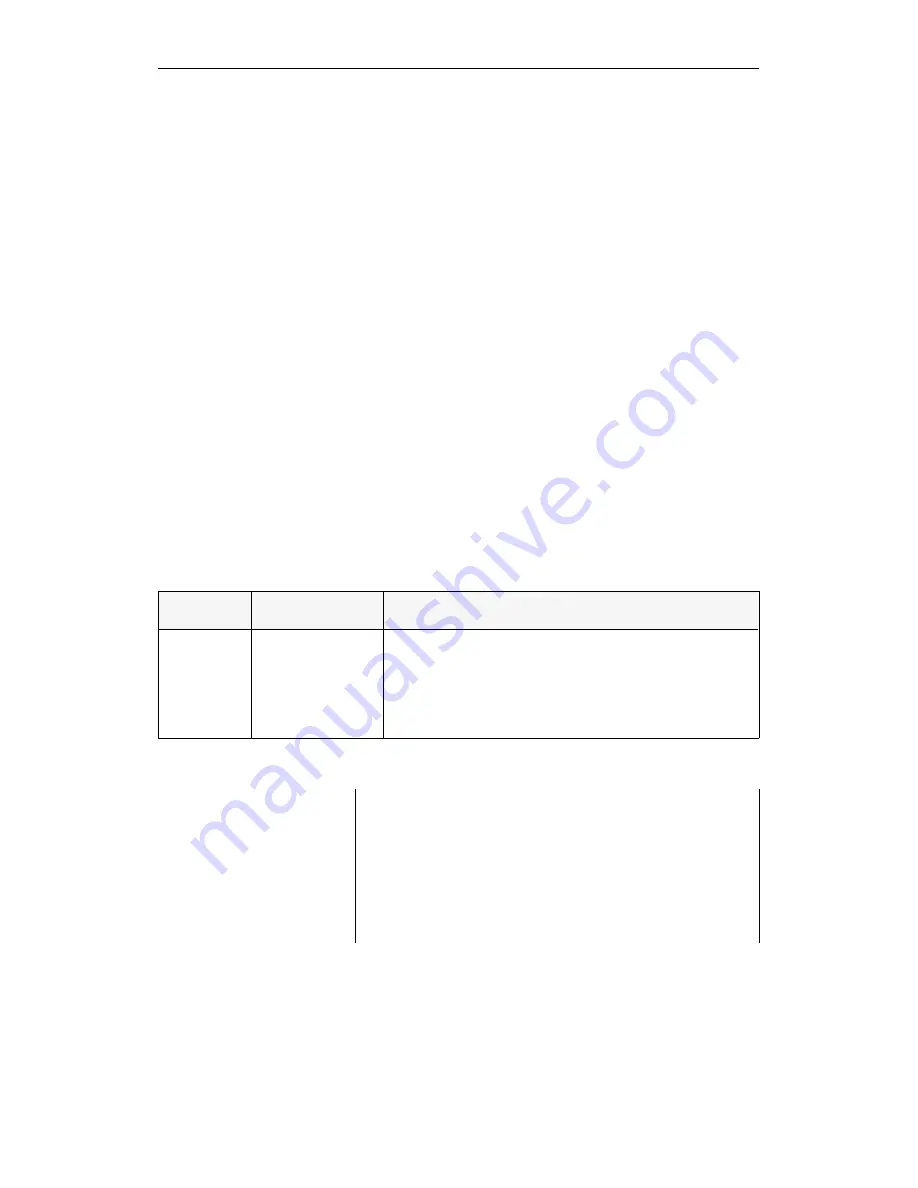

SED/SEE disable/enable

semaphore

(non-system operations)

Operation

Operand

Function

SED

SEE

0 to 31

0 to 31

Disable (set) a semaphore

Enable (release) a semaphore

evaluation of the result of the operation via

CC 0/CC 1

Note

The SED xx and SEE xx operations must be programmed in all

CPUs that require synchronized access to a common global

memory area.

Standard FBs, handling blocks and blocks for multiprocessor

communication manage the coordination internally. If you use

these blocks, you do not need to program the operations SEE xx

and SED xx.

Table 3-29

Disable/enable semaphore

Semaphore Operations

CPU 948 Programming Guide

C79000-G8576-C848-04

3 - 75

Summary of Contents for CPU 948

Page 10: ...Contents CPU 948 Programming Guide 1 2 C79000 G8576 C848 04 ...

Page 32: ...Contents CPU 948 Programming Guide 2 2 C79000 G8576 C848 04 ...

Page 72: ...Data Blocks CPU 948 Programming Guide 2 42 C79000 G8576 C848 04 ...

Page 74: ...Contents CPU 948 Programming Guide 3 2 C79000 G8576 C848 04 ...

Page 154: ...Contents CPU 948 Programming Guide 4 2 C79000 G8576 C848 04 ...

Page 200: ...Contents CPU 948 Programming Guide 5 2 C79000 G8576 C848 04 ...

Page 308: ...Contents CPU 948 Programming Guide 7 2 C79000 G8576 C848 04 ...

Page 324: ...Examples of Parameter Assignment CPU 948 Programming Guide 7 18 C79000 G8576 C848 04 ...

Page 326: ...Contents CPU 948 Programming Guide 8 2 C79000 G8576 C848 04 ...

Page 370: ...Addressable System Data Area CPU 948 Programming Guide 8 46 C79000 G8576 C848 04 ...

Page 372: ...Contents CPU 948 Programming Guide 9 2 C79000 G8576 C848 04 ...

Page 486: ...Contents CPU 948 Programming Guide 11 2 C79000 G8576 C848 04 ...

Page 522: ...PG Functions via the S5 Bus CPU 948 Programming Guide 11 38 C79000 G8576 C848 04 ...

Page 524: ...Contents CPU 948 Programming Guide 12 2 C79000 G8576 C848 04 ...

Page 538: ...Contents CPU 948 Programming Guide 13 2 C79000 G8576 C848 04 ...

Page 546: ...List of Key Words CPU 948 Programming Guide Index 6 C79000 G8576 C848 04 ...