S/AI

Hardware Reference

Page 17 of 52

3.5 GPIO Interface

It is possible to use the programmable digital I/Os GPIO[0:14] on the S. Their behavior

has to be defined project specific in the firmware.

Unused GPIO pins shall be left unconnected to stay compatible. There may be functions assigned

to some in future versions of the firmware.

3.6 I

2

C Interface

The I

2

C bus interface serves as an interface between the internal microcontroller and the serial I

2

C

bus. S is the master and controls all I

2

C bus specific sequencing, protocol and timing. It

supports standard (100kHz) and fast (400kHz) speed modes. The S as an I

2

C master

must be the only master of the I

2

C bus (no

multimaster

capability). Clock stretching is supported.

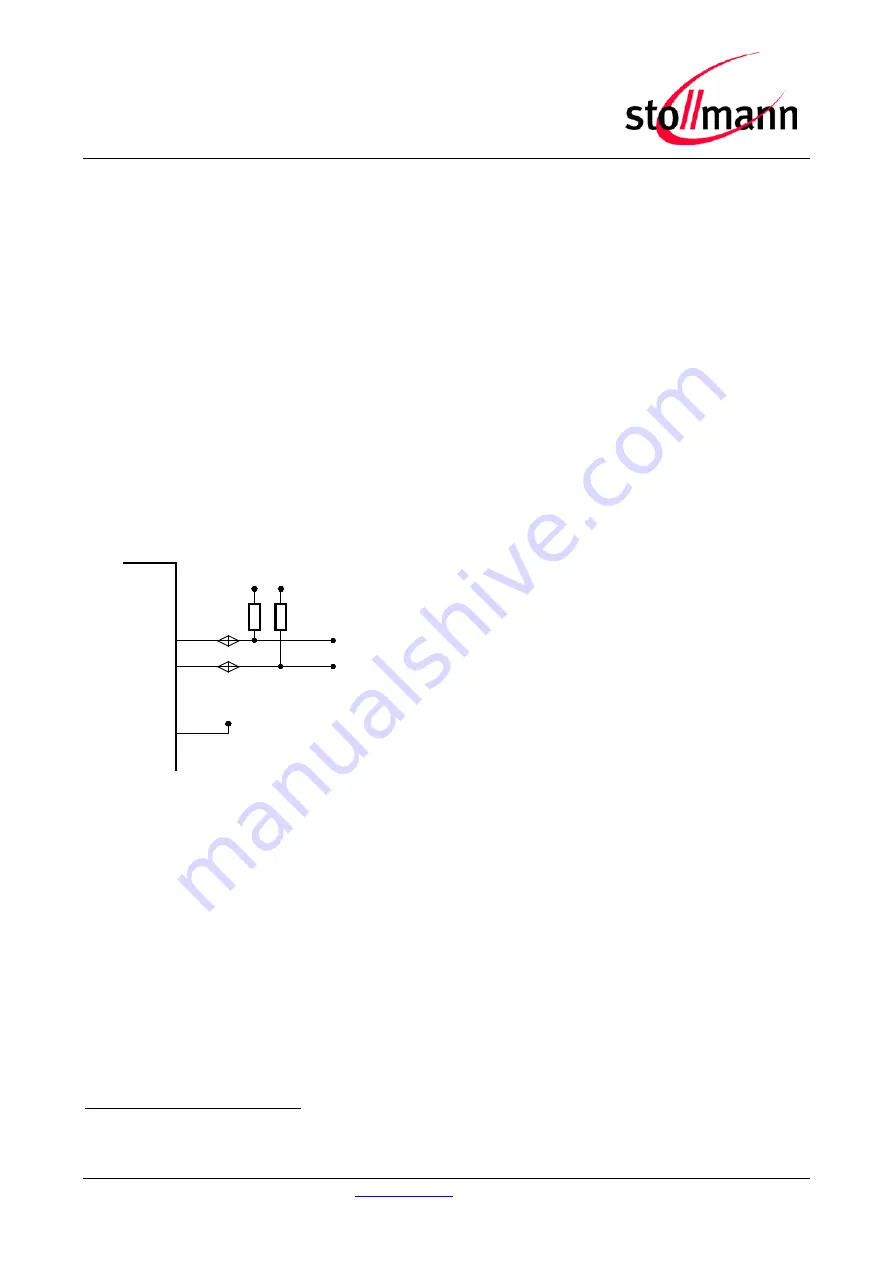

GPIO[1]/I2C-SDA and GPIO[0]/I2C-SCL can be used to form an I

2

C interface. It is required to

connect 4k7 pull-up resistors on I2C-SCL and I2C-SDA when this interface is used.

I2C-SCL

I2C-SDA

GPIO[0]/I2C-SCL

GPIO[1]/I2C-SDA

S

VSUP

Rpu

+3.3V

B-2

D-3

E-6,F-6

+3.3V

Rpu

+3.3V

4k

7

4k

7

Figure 7: S I

2

C Interface

1

subject to firmware support, contact Stollmann for current status