S42

Hardware User Guide

1VV0301303 Rev. 11

Page 25 of 85

2021-05-06

Not Subject to NDA

3.5.

I

2

C Interface

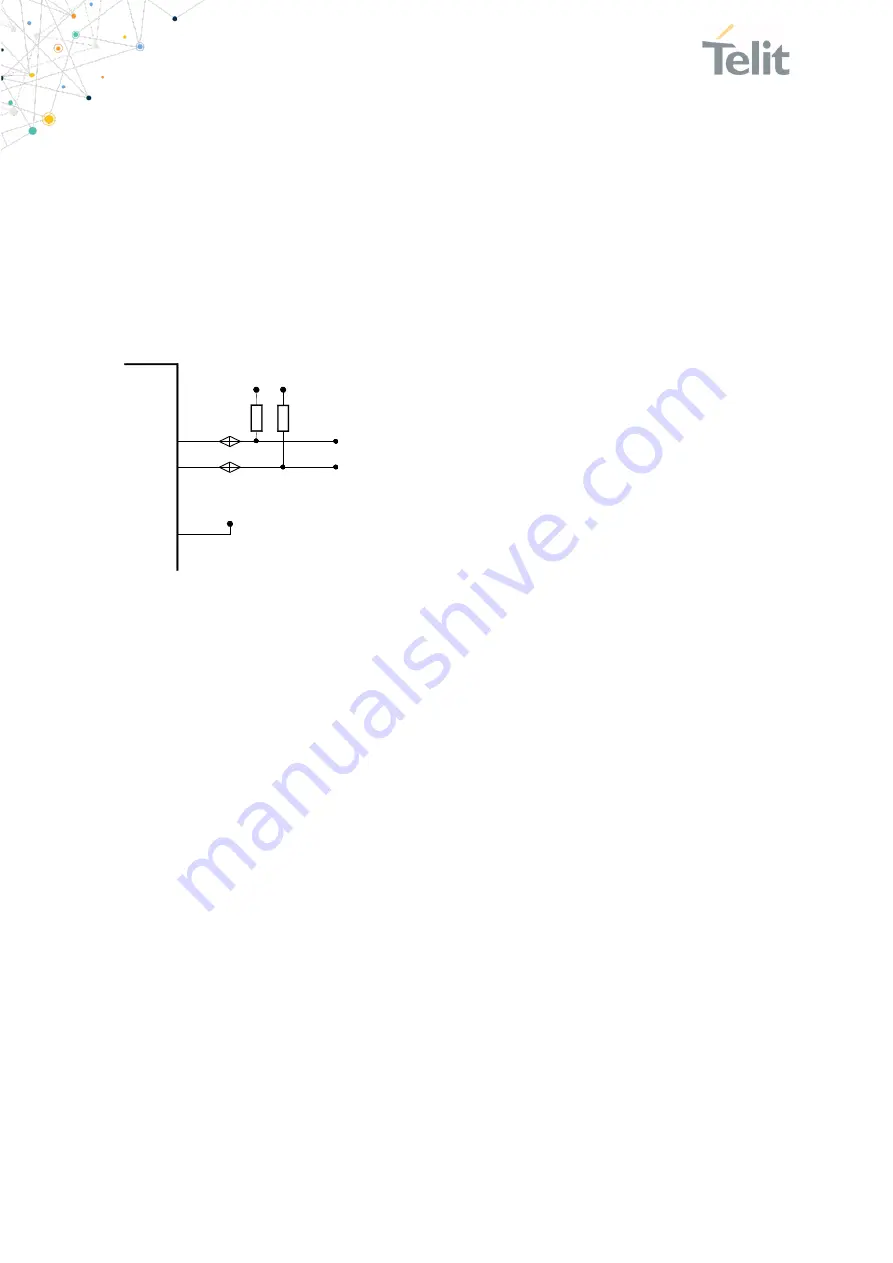

The I

2

C bus interface serves as an interface between the internal microcontroller and the

serial I

2

C bus. S42 is the master and controls all I

2

C bus specific sequencing,

protocol, and timing. It supports standard (100kHz) and fast (400kHz) speed modes. The

S42 as an I

2

C master must be the only master of the I

2

C bus (no

multimaster

capability). Clock stretching is supported.

GPIO[1]/I2C-SDA and GPIO[0]/I2C-SCL can be used to form an I

2

C interface. It is required

to connect 4k7 pull-up resistors on I2C-SCL and I2C-SDA when this interface is used.

I2C-SCL

I2C-SDA

GPIO[0]/I2C-SCL

GPIO[1]/I2C-SDA

S42

VSUP

Rpu

+3.3V

B-2

D-3

E-6,F-6

+3.3V

Rpu

+3.3V

4k7

4k7

Figure 12: S42 I

2

C Interface

3.6.

SPI Serial Peripheral Interface

The serial peripheral interface (SPI) allows for full-duplex, synchronous, serial

communication with external devices. The interface can be configured as the

master and

then provides the communication clock (SCK) to the external slave device(s), or as the

slave. The SPI Interface supports SPI-modes 0 through 3. Module pins are used as

follows:

•

GPIO[2]: SPI-MOSI

•

GPIO[5]: SPI-MISO

•

GPIO[8]: SPI-SCK