PPM-C412/Configuration

v1.0

www.winsystems.com

Page 20

7.5 DOS Legacy Memory Map

7.6 Memory Shadowing

Any block of memory that can be designated as read only or write only can be

“shadowed” into DRAM memory. Typically, this is done to allow ROM code to execute

more rapidly out of main DRAM. ROM is used as read only during the copy process

while DRAM at the same time is designated write only. After copying, the DRAM is

designated read only so that ROM is shadowed. CPU bus transactions are routed

accordingly. The PMC does not respond to transactions originating from PCI or ISA

masters and targeted at shadowed memory blocks.

7.7 I/O Address Space

The SoC positively decodes accesses to all internal registers, including PCI

configuration registers (CF8h and CFCh), PC/AT compatible I/O registers (8237, 8254,

and 8259), and all relocatable I/O space registers (UART).

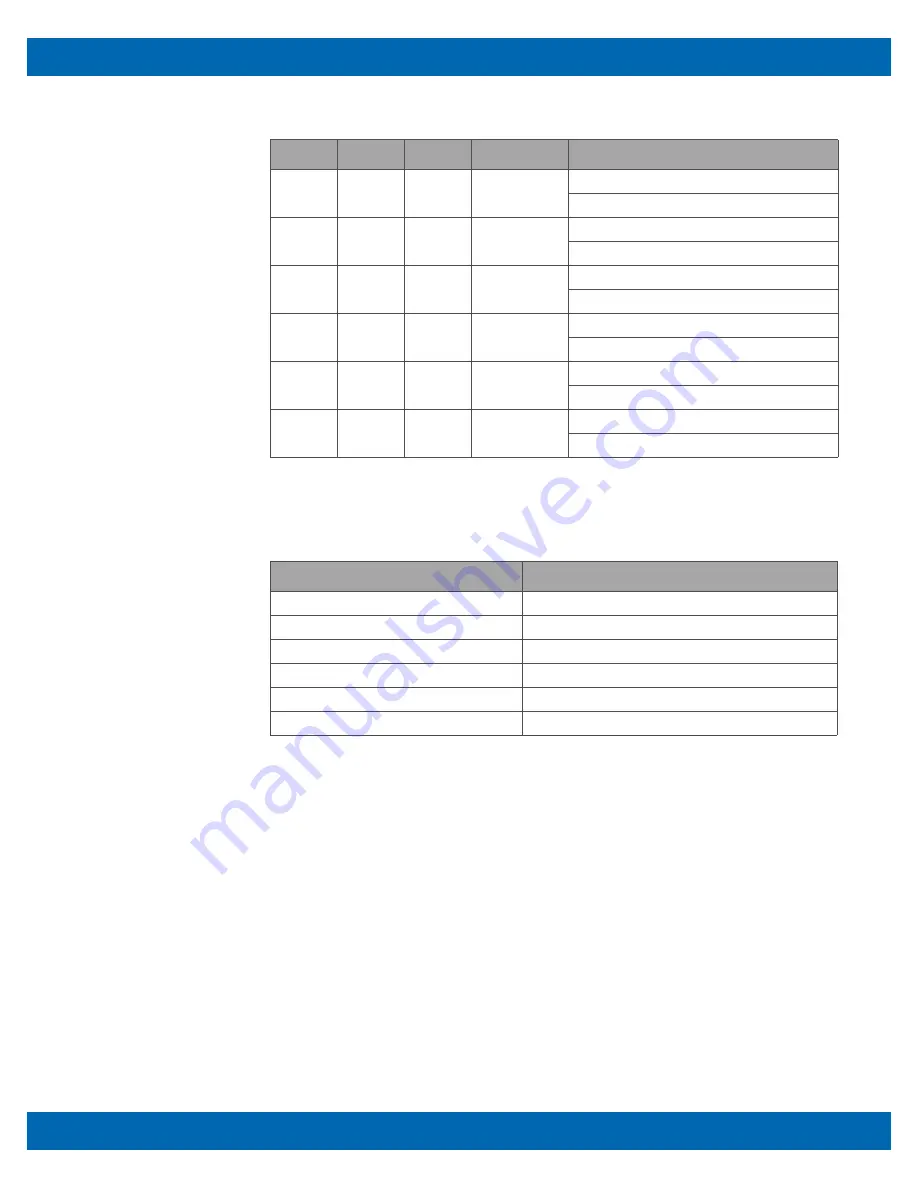

Table 9:

External devices

Bus

Device Function

Device ID

Device/Function Description

3

0

0

104Ch

Device: 8240

Function: PCI/PCI bridge

5

0

0

12D8h

Device: 2304

Function: PCI/PCI bridge

6

1

0

12D8h

Device: 2304

Function: PCI/PCI bridge

6

2

0

12D8h

Device: 2304

Function: PCI/PCI bridge

7

0

0 8086h

Device:

8086

Function: Intel Ethernet controller

8

0

0 8086h

Device:

8086

Function: Intel Ethernet controller

Table 10:

Hex ranges

Hex Range

Usage

0000:0000-0009:FFFF

Main memory (DOS area)

000A:0000-000B:FFFF

Legacy video area (SMM memory)

000C:0000-000D:FFFF

Expansion area

000E:0000-000E:FFFF

Extended system BIOS (lower)

000F:0000-000F:FFFF

System BIOS (upper)

0010:0000-7FFF:FFFF

Main memory