26

Registers

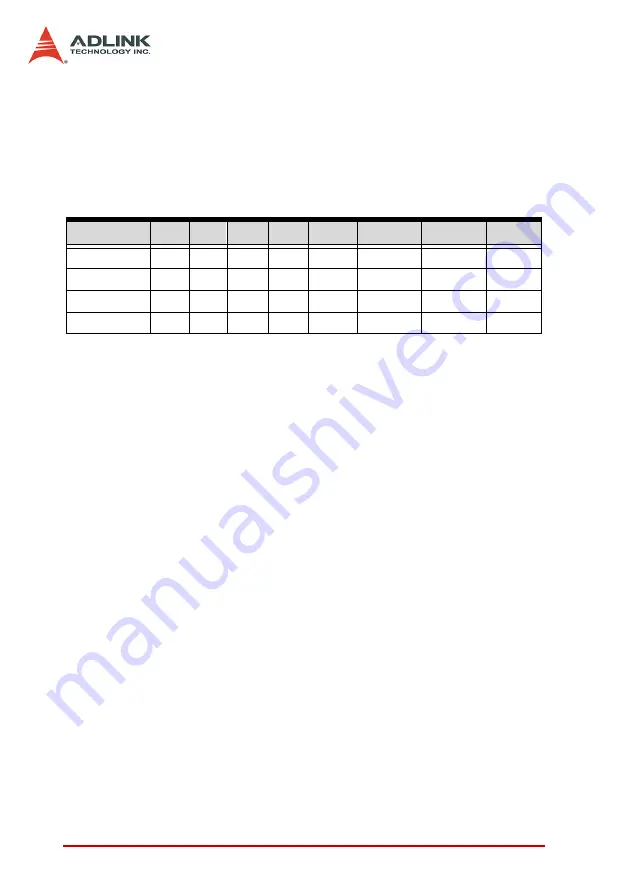

4.8 FIFO Status Register

This register is used to monitor some status of the PCI-9812/10.

Address:

BASE + 18h

Attribute:

read

Data Format:

Bit 0 -- FIFOIR, FIFO input ready flag.

0: The FIFO is not ready for input, indicating FIFO is full

1: The FIFO is ready for input (not full).

Bit 1 -- FIFOHF, FIFO half full flag.

0: The FIFO is not half full yet.

1: The FIFO is at least half full.

Bit 2 -- FIFOOR, FIFO output ready flag

0: The FIFO is not ready for output, indicating FIFO is

empty.

1: The FIFO is ready for output (not empty).

Bit 3 -- PTC0, post trigger counter is 0

0: The post trigger counter is not 0.

1: The post trigger counter reaches 0.

Bit 4 -- TD, trigger detection flag

0: The trigger condition is not met yet no trigger is detected.

1: Trigger is detected.

Bit

7

6

5

4

3

2

1

0

BASE+18h

---

---

ACQ TD PTCO FIFOOR FIFOHF FIFOIR

BASE+19h

---

---

---

---

---

---

---

---

BASE+1Ah

---

---

---

---

---

---

---

---

BASE+1Bh

---

---

---

---

---

---

---

---

Summary of Contents for NuDAQ PCI-9810

Page 4: ......

Page 10: ...vi ...

Page 19: ...Installation 9 2 3 PCI 9812 10 s Layout Figure 2 1 PCB Layout of the PCI 9812 10 ...

Page 22: ...12 ...

Page 40: ...30 ...

Page 78: ...68 Software Utility ...