Bit

Decimal

Value

Definition

6

Not used

0

Always be 0.

7

PON

128

Power-on detection. Power has been

turned off and on since the last time the

event register was read or cleared.

3.3

Status Byte Register

The status byte register reports the status information of other status registers. Query

data waiting in the output buffer of the power supply is immediately reported

through the bit4 (MAV, Message Available Bit) of the status byte register. Bits in the

SUMMARY register of the status byte register are not latched. Clearing an event

register will clear the corresponding bits in the status byte SUMMARY register.

Reading all messages in the output buffer, including pending queries, will clear the

bit4 (MAV, Message Available Bit). The definitions of the bits in the status byte

register and the decimal values corresponding to their binary weights are as shown in

the table below.

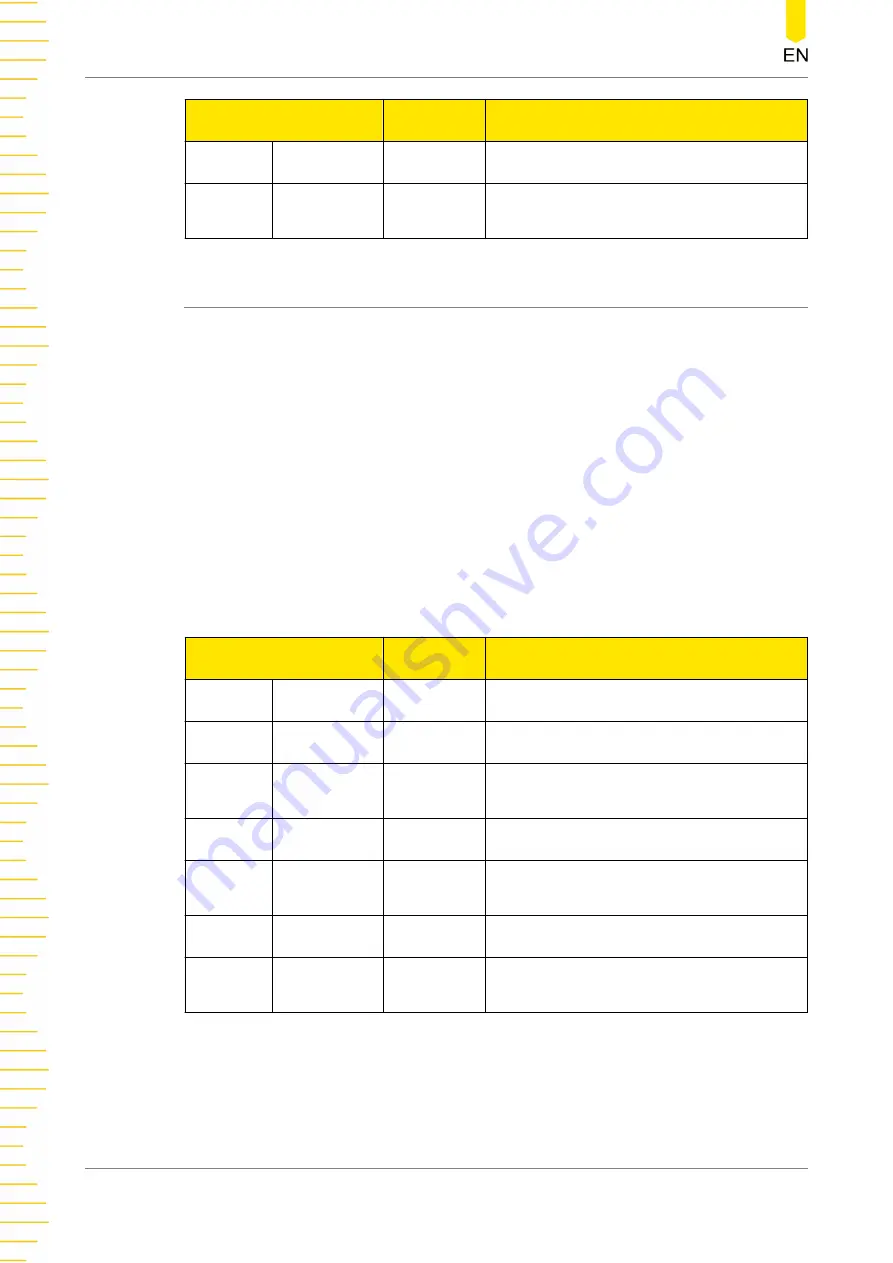

Table 3.5 Definitions of the bits in the status byte register and the decimal values

corresponding to their binary weights

Bit

Decimal

Value

Definition

0-1

Not used

0

Always be 0.

2

ERR

4

One or more errors have been stored in the

Error Queue.

3

QUES

8

One or more bits are set in the

questionable status register (bits must be

enabled in the enable register).

4

MAV

16

Data is available in the power supply

output buffer.

5

ESB

32

One or more bits are set in the standard

event register (bits must be enabled in the

enable register).

6

RQS

64

The power supply is requesting service.

7

OPER

128

One or more bits are set in the operation

event register (bits must be enabled in the

enable register).

SCPI Status Register

12

Copyright ©RIGOL TECHNOLOGIES CO., LTD. All rights reserved.

Summary of Contents for DP900 Series

Page 1: ......

Page 133: ...d Exit Programming Examples Copyright RIGOL TECHNOLOGIES CO LTD All rights reserved 125 ...

Page 141: ......