Hardware Description

18

The SSC supports many serial synchronous communication protocols generally used in

audio and telecom applications such as I2S, Short Frame Sync, Long Frame Sync, etc.

The SSC has separated receive and transmit channels. Each channel has a data, a clock

and a frame synchronization signal (RD, RK, RF, resp. TD, TK, TF). Both a receive and a

transmit DMA channel are assigned to each SSC.

4.29. AC97 Controller (AC97C)

AC97 Component Specification 2.2 compliant AC97 digital controller. It supports mono or

stereo up to 20 bit sample length and features a sampling rate up to 48 KHz.

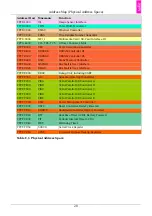

Pin

Description

Type

AC97CK

12.288-MHz bit-rate clock

Input

AC97RX

SDATA_IN

Input

AC97FS

48-KHz frame indicator

Output

AC97TX

SDATA_OUT

Output

Table 4.4. AC97 I/O Lines

4.30. Image Sensor Interface (ISI)

The Image Sensor Interface (ISI) supports direct connection to the ITU-R BT. 601/656 8-

bit mode compliant sensors and up to 12-bit grayscale sensors. It receives the image data

stream from the image sensor on the 12-bit data bus. This module receives up to 12 bits

for data, the horizontal and vertical synchronizations and the pixel clock. The reduced pin

count alternative for synchronization is supported for sensors that embed SAV (start of

active video) and EAV (end of active video) delimiters in the data stream.

The Image Sensor Interface interrupt line is generally connected to the Advanced

Interrupt Controller and can trigger an interrupt at the beginning of each frame and at

the end of a DMA frame transfer. If the SAV/EAV synchronization is used, an interrupt can

be triggered on each delimiter event.

For 8-bit color sensors, the data stream received can be in several possible formats: YCbCr

4:2:2, RGB 8:8:8, RGB 5:6:5 and may be processed before the storage in memory. The

data stream may be sent on both preview path and codec path if the bit CODEC_ON in the

ISI_CR1 is one. To optimize the bandwidth, the codec path should be enabled only when

a capture is required.

In grayscale mode, the input data stream is stored in memory without any processing. The

12-bit data, which represent the grayscale level for the pixel, is stored in memory one or

two pixels per word, depending on the GS_MODE bit in the ISI_CR2 register. The codec

datapath is not available when grayscale image is selected.

4.31. LCD controller

The LCD controller supports single and double scan monochrome and color passive

STN LCD modules and single scan active TFT LCD modules with a resolution of up to

2048x2048 with a color depth of up 24 bits per pixel.