15. USART

MC97F6108A User’s manual

156

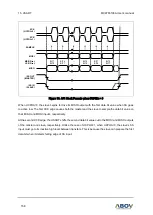

As described already, when Receiver clock is synchronized to the start bit, the data recovery can begin.

Data recovery process is almost similar to the clock recovery process. The data recovery logic samples

16 times for each incoming bits for Normal mode and 8 times for Double Speed mode. It uses the

samples 8, 9, and 10 to decide data value for Normal mode, and the samples 4, 5, and 6 for Double

Speed mode.

If more than 2 samples have low levels, the received bit is considered to a logic 0. If more than 2

samples have high levels, the received bit is considered to a logic 1. The data recovery process is then

repeated until a complete frame is received including the first stop bit. The decided bit value is stored

in the receive shift register in order. Note that Receiver only uses the first stop bit of a frame. Internally,

after receiving the first stop bit, Receiver is in idle state and waiting to find start bit.

Figure 71. Sampling of Data and Parity Bit

A process for detecting stop bit is similar to the clock and data recovery process. That is, if 2 or more

samples of 3 center values have high level, correct stop bit is detected. If not, a Frame Error flag will be

set. After deciding whether a valid stop bit is received or not, the Receiver enters into idle state and

monitors the RXD2 line to check a valid high to low transition is detected (start bit detection).

Figure 72. Stop Bit Sampling and Next Start Bit Sampling

RxD2

1

2

3

4

5

6

7

8

9

10

11

12 13

14 15

16

1

BIT n

1

2

3

4

5

6

7

8

1

Sample

(U2X = 0)

Sample

(U2X = 1)

RxD2

1

2

3

4

5

6

7

8

9

10

11

12 13

STOP 1

1

2

3

4

5

6

7

Sample

(U2X = 0)

Sample

(U2X = 1)

(A)

(B)

(C)