UG-1262

Rev. B | Page 185 of 312

FLASH CONTROLLER

FLASH CONTROLLER FEATURES

The

processor includes 128 kB of embedded flash memory available for access through the flash controller. The embedded

flash has a 72-bit wide data bus, providing two 32-bit words of data and one corresponding 8-bit ECC byte per access.

The flash controller is coupled with a cache controller module that provides two Arm high speed bus (AHB) ports: one port for reading

data (DCode), and the other for reading instructions (ICode). A prefetch mechanism is implemented in the flash controller to optimize

ICode read performance.

Flash writes are supported by a keyhole mechanism through Arm peripheral bus (APB) writes to memory mapped registers. The flash

controller includes support for DMA-based keyhole writes.

FLASH CONTROLLER OVERVIEW

Key flash controller features include the following:

The prefetch buffer provides optimal performance when reading consecutive addresses on the ICode interface.

Simultaneous ICode and DCode read accesses. DCode has priority on contention. Simultaneous reads are possible if ICode returns

buffered data from prefetch.

DMA based keyhole writes, including address auto-increment for sequential accesses.

ECC for error detection and correction. Errors and corrections may be reported as bus errors on the ICode or DCode bus as

interrupts or ignored.

SUPPORTED COMMANDS

The following is a summary of the commands supported by the flash controller:

Read. Supported through the ICode and DCode interfaces.

Write. Provided by a keyhole mechanism through memory mapped registers.

Mass erase. Clears all user data and program code.

Page erase. Clears user data or program code from a 2 kB page in flash.

Signature. Generates and verifies signatures for any set of contiguous whole pages of user data or program code.

Abort. Terminates a command in progress.

PROTECTION AND INTEGRITY FEATURES

Protection and integrity features include the following:

A fixed user key is required for running protected commands including mass erase and page erase.

Optional and user definable write protection for user accessible memory.

Optional 8-bit ECC. Enabled by user code, off by default.

FLASH CONTROLLER OPERATION

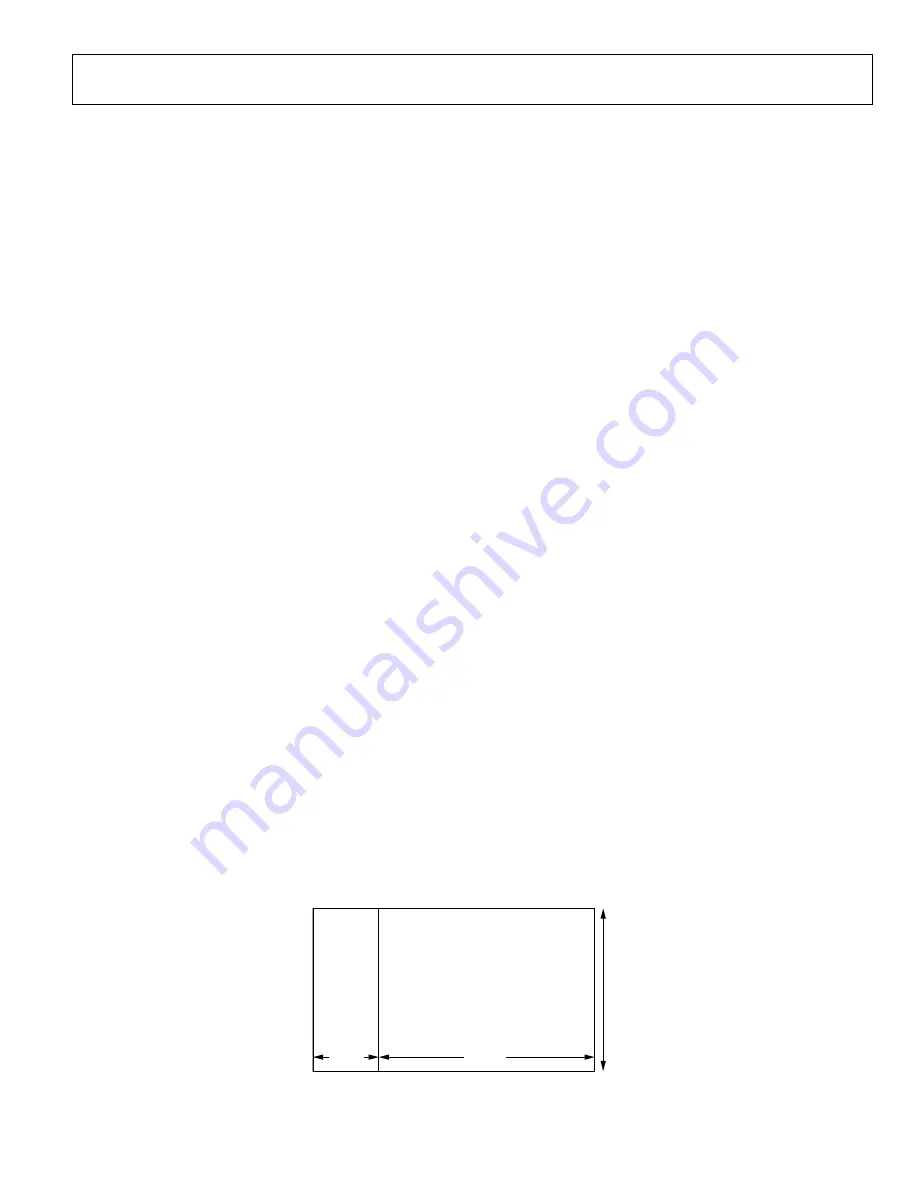

A flash block of 128 kB is available for user code and data, from 0 to 0x1FFFF. It is not possible to execute flash while erasing a flash page

at the same time. The flash provides a 64-bit data bus, plus eight bits for corresponding ECC metadata. The memory is organized as a

number of pages, each 2 kB in size, as well as 256 bytes reserved for ECC. See Figure 49 for details on flash, and Figure 50 for a full over

overview of the flash page structure.

ONE PAGE

DATA

2kB

ECC

256 bytes

8 BITS

64 BITS

256

1667

5-

03

2

Flash Page Structure