UG-1262

Rev. B | Page 37 of 312

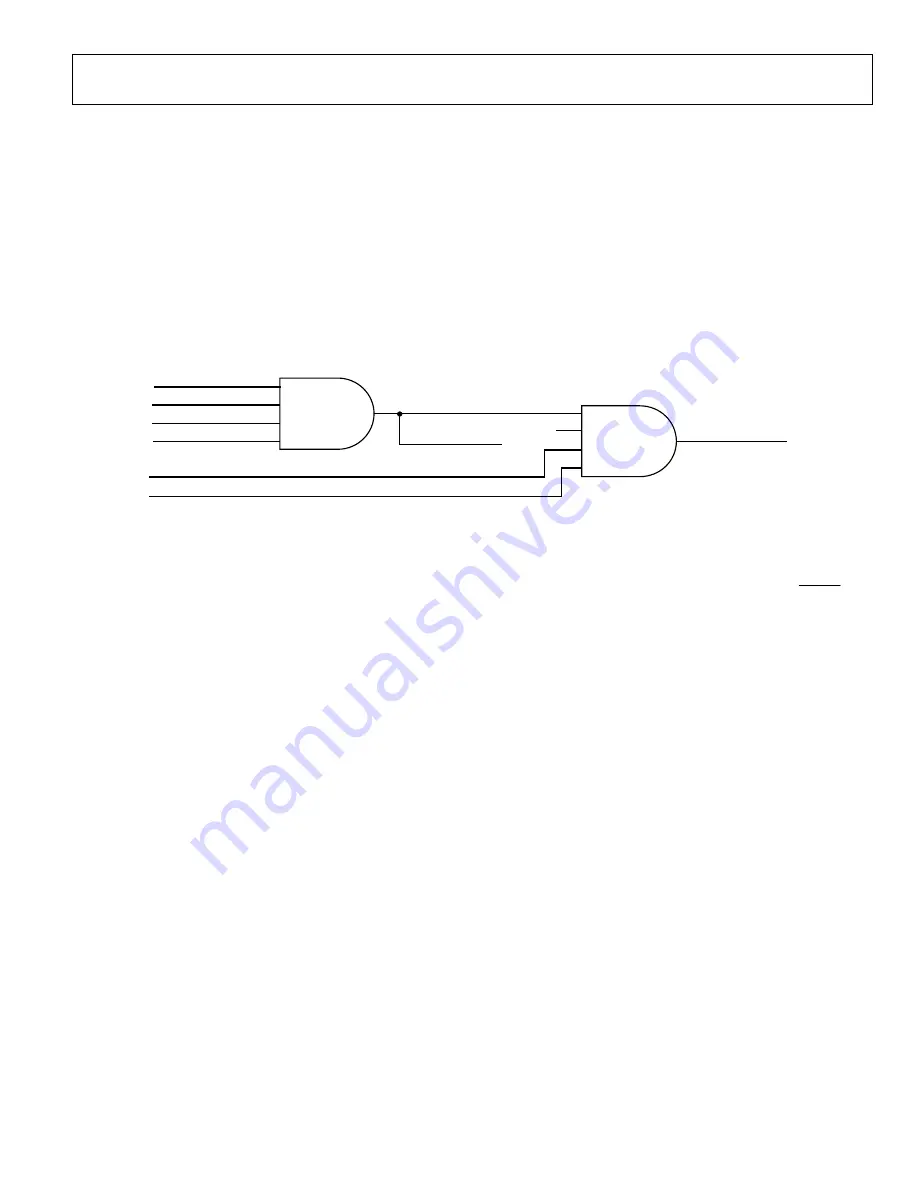

SYSTEM RESETS

There are three primary reset sources on the digital die, as shown in Figure 4. A digital die watchdog timer is also available, but is

disabled by default. These reset sources are as follows:

External reset.

POR.

Software reset.

In addition, there are four similar reset sources on the analog die, as follows:

External reset.

POR.

Software reset of digital device.

Watchdog timer reset.

RESET ANALOG DEVICE

RESET DIGITAL DEVICE

DIGITAL DEVICE EXTERNAL RESET

AFE WDT RESET

AFE SOFTWARE RESET

DIGITAL DEVICE SOFTWARE RESET

EXTERNAL RESET

DIGITAL DEVICE POWER ON RESET

AFE POR

16

67

5-

0

05

Figure 4. Reset Sources of the

The analog die POR and digital die POR are differentiated due to separate power supplies. Two AFE reset sources are also reported to the

digital die as an external reset.

On both die, a POR circuit is present. If either POR circuit triggers, the entire chip resets and all control registers and circuitry return to

their default state. Likewise, both die have an external reset. The external pin reset or hardware reset occurs when the external RESET pin

is pulled low. All circuits and control registers return to their default states. The analog die watchdog timer reset circuit generates a reset

if it is not refreshed correctly. By default, a watchdog timer reset resets all circuits and control registers.

The RST_STAT register indicates the source of the last reset to the digital die. This register can be used during a reset exception service

routine to identify the source of the reset to the digital die. The RSTSTA register indicates the source of the last reset to the analog die.

The RSTSTA register can be used during a reset exception service routine to identify the source of the reset to the analog die.

After a reset sequence, the on-chip kernel completes a self check of the analog die. Though problems are unlikely, if an issue occurs,

AFEDIESTA, Bit 0 sets to 1. After every reset, read this bit. If this bit is read as 1, do not continue with analog die operations.

DIGITAL DIE RESET OPERATION

The software system reset is provided as part of the Arm Cortex-M3 processor. To generate a software system reset, call the

NVIC_SystemReset() function. This function effectively writes 0x05FA to the 16 MSBs of the Cortex register, AIRCR, Address

0xE000ED0C. The NVIC_SystemResert() function, along with other useful functions, are defined in the Cortex microcontroller software

interface standard (CMSIS) header files that are provided with the tools from third party vendors. The NVIC_SystemReset() function is

defined in the

core_cm3.h

file.

The RST_STAT register stores the cause for the reset until it is cleared by writing to the same register. The RST_STAT register can be

used during a reset exception service routine to identify the source of the reset. The watchdog timer is enabled by default after a reset.

Table 33 lists details of all reset types.