UG-1262

Rev. B | Page 202 of 312

All write protection is cleared on a POR, but the Analog Devices bootloader reasserts write protection (as defined by the WRPROT

word) in user space before enabling user access to the flash array. Removing write protection can only be performed by an erase page

command of the most significant page in user space (provided that page is not currently protected) or by a mass erase command.

Following a completed mass erase command, all protection of pages in user space is immediately cleared. The user can write to user

space immediately following such an erase without a device reset required.

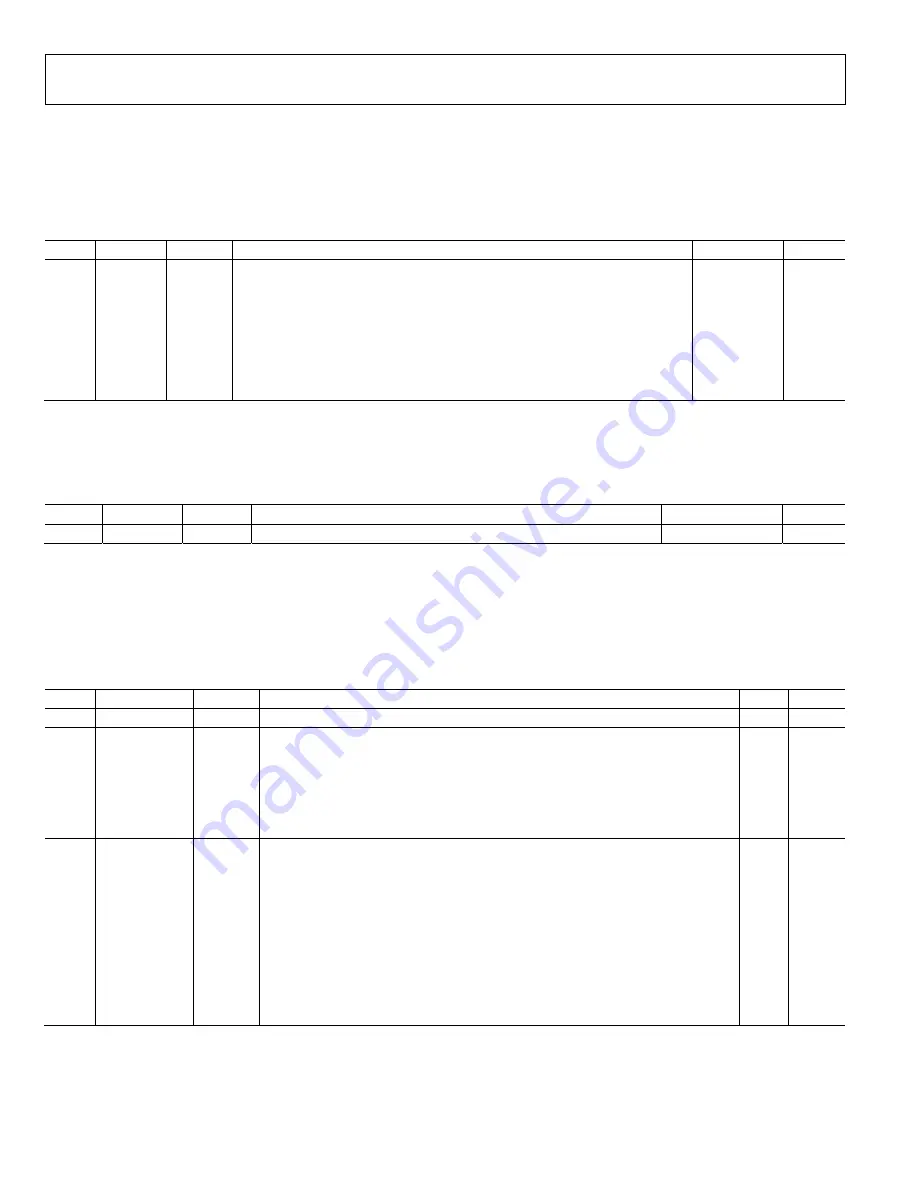

Table 234. Bit Descriptions for WRPROT

Bits Bit

Name

Settings

Description

Reset

Access

[31:0] WORD

Clear Bits to Write Protect Related Groups of User Space Pages. After cleared,

these bits can only be set again by resetting the device. Each bit of this 32-bit

word represents a 32nd of the total available user space. For 256 kB parts

consisting of 2 kB pages (128 pages), each bit represents the write protection

state of a group of four pages. For 128 kB parts consisting of 2 kB pages

(64 pages), each bit represents the write protection state of a group of two

pages. For 64 kB parts consisting of 2 kB pages (32 pages), each bit represents

the write protection state of a single page. The most significant bit of this

register corresponds to the most significant group of pages in user space.

0xFFFFFFFF R/W0C

SIGNATURE REGISTER

Address: 0x4001802C, Reset: 0xXXXXXXXX, Name: SIGNATURE

Table 235. Bit Descriptions for SIGNATURE

Bits Bit

Name

Settings

Description

Reset

Access

[31:0]

VALUE

Provides Read Access to the Most Recently Generated Signature.

0xXXXXXXXX

R

USER CONFIGURATION REGISTER

Address: 0x40018030, Reset: 0x00000000, Name: UCFG

User key is required. Write to this register to enable user control of DMA and auto-increment features. When user code has finished

accessing this register, write arbitrary data to the key register to reassert protection.

Table 236. Bit Descriptions for UCFG

Bits Bit

Name

Settings Description

Reset Access

[31:2] Reserved

Reserved.

0x0 R

1 AUTOINCEN

Automatic Address Increment for Keyhole Access. When this bit is set, KH_ADDR

automatically increments by 0x8 during each write command or after each read

command, enabling user code to write a series of sequential flash locations

without having to manually set the flash address for each write. The KH_ADDR

register is incremented, and can be observed by user code when STAT, Bit 5 is

asserted during a write command or after a read command. When this bit is set,

user code cannot directly modify KH_ADDR.

0x0 R/W

0 KHDMAEN

Keyhole DMA Enable. The flash controller interacts with the DMA controller when

this bit is set. Prior to setting this bit, write the starting address to the KH_ADDR

register. Then configure the DMA controller to write data to the KH_DATA1

register (address must be data word aligned), to always write pairs of 32-bit words

(R_POWER = 1), and to write an integer number of data pairs (for an odd number

of words, user code must write one word manually without the help of DMA). All

DMA writes automatically increment the target address (similar to the behavior of

UCFG, Bit 1). The DMA controller can only be used to write sequential addresses

starting from the value of KH_ADDR. The flash controller automatically begins

write operations each time the DMA controller provides a pair of words to write.

Interaction with the DMA controller is designed to use burst writes, which can

significantly reduce overall programming time.

0x0 R/W