UG-1262

Rev. B | Page 236 of 312

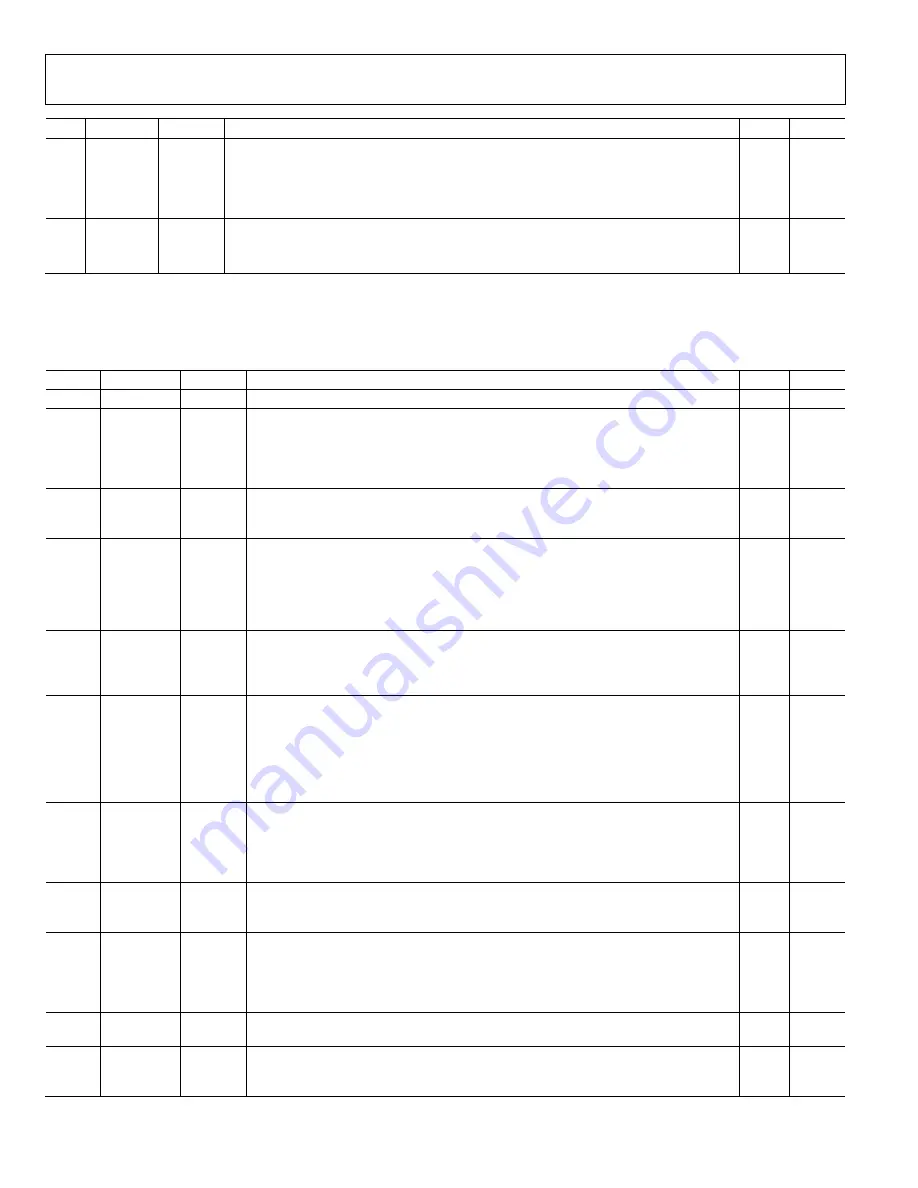

Bits Bit

Name Settings Description

Reset Access

1 ADR10EN

Enabled 10-Bit Addressing. If this bit is clear, the slave can support four slave addresses,

programmed in the ID0 register to the ID3 register. When this bit is set, 10-bit addressing

is enabled. One 10-bit address is supported by the slave and is stored in ID0 and ID1, where

ID0 contains the first byte of the address and the upper 5 bits must be programmed to 11110.

ID3 and ID4 can be programmed with 7-bit addresses at the same time.

0x0 R/W

0 SLVEN

Slave

Enable.

0x0 R/W

0

Slave disabled and slave state machine flops are held in reset.

1

Slave

enabled.

SLAVE I

2

C STATUS, ERROR, AND IRQ REGISTER

Address: 0x4000302C, Reset: 0x0001, Name: SSTAT

Table 293. Bit Descriptions for SSTAT

Bits

Bit

Name Settings Description

Reset Access

15 Reserved

Reserved.

0x0 R

14 START

Start and Matching Address. This bit is asserted if a start is detected on the I2C_SCL and

I2C_SDA and the device address matches, if a general call code (address = 00000000) is

received and general call is enabled, if a high speed code (address = 00001XXX) is

received, or if a start byte (00000001) is received. It is cleared on receipt of either a

stop or start condition.

0x0 R

13 REPSTART

Repeated Start and Matching Address. This bit is asserted if a start is already asserted

and then a repeated start is detected. It is cleared when read or on receipt of a stop

condition. This bit can drive an interrupt.

0x0 RC

[12:11]

IDMAT

Device ID Matched.

0x0

R

00

Received address matched ID Register 0.

01

Received address matched ID Register 1.

10

Received address matched ID Register 2.

11

Received address matched ID Register 3.

10 STOP

Stop After Start and Matching Address. This bit is set by hardware if the slave device

receives a stop condition after a previous start condition and a matching address. Cleared

by a read of the status register. If SCTL, Bit 8 in the slave control register is asserted, the

slave interrupt request asserts when this bit is set. This bit can drive an interrupt.

0x0 RC

[9:8] GCID

General ID. This bit is cleared when SCTL, Bit 4 is set to 1. These status bits are not

cleared by a general call reset.

0x0 R

00

No general call.

01

General call reset and program address.

10

General call program address.

11

General call matching alternative ID.

7 GCINT

General Call Interrupt. This bit always drives an interrupt. The bit is asserted if the

slave device receives a general call of any type. To clear, write 1 to the GCSBCLR in

the slave control register. If the call was a general call reset, all registers are at their

default values. If the call was a hardware general call, the receive FIFO holds the

second byte of the general call, which can be compared with the ALT register.

0x0 R

6 SBUSY

Slave Busy. Set by hardware if the slave device receives an I

2

C start condition. Cleared

by hardware when the address does not match an ID register, the slave device

receives an I

2

C stop condition, or if a repeated start address does not match.

0x0 R

5 NOACK

Acknowledge Not Generated by the Slave. When asserted, this bit indicates that the slave

responded to its device address with a no acknowledge. This bit is asserted if there was

no data to transmit and the sequence was a slave read or if the no acknowledge bit was

set in the slave control register and the device was addressed. This bit is cleared on a

read of the SSTAT register.

0x0 RC

4 SRXOF

Slave Receive FIFO Overflow. Asserts when a byte is written to the slave receive FIFO

and the FIFO is already full.

0x0 RC

3 SRXREQ

Slave Receive Request. This bit asserts whenever the slave receive FIFO is not empty. Read

or flush the slave receive FIFO to clear this bit. This bit asserts on the falling edge of the

I2C_SCL clock pulse that clocks in the last data bit of a byte. This bit can drive an interrupt.

0x0 RC