36

ATmega103(L)

0945G–09/01

The clock source for Timer/Counter0 prescaler is named PCK0. PCK0 is by default con-

nected to the main system clock CK. Observe that CPU clock frequency can be lower

than the XTAL frequency if the XTAL divider is enabled. By setting the AS0 bit in ASSR,

Timer/Counter0 prescaler is asynchronously clocked from the TOSC1 pin. This enables

use of Timer/Counter0 as a Real-time Clock (RTC). A crystal can be connected between

t he T OS C 1 a n d TO S C2 p i n s t o s e r ve a s a n i n d ep e n d e n t c l o c k s o u rc e fo r

Timer/Counter0. This oscillator is optimized for use with a 32.768 kHz crystal.

8-bit Timer/Counters

T/C0 and T/C2

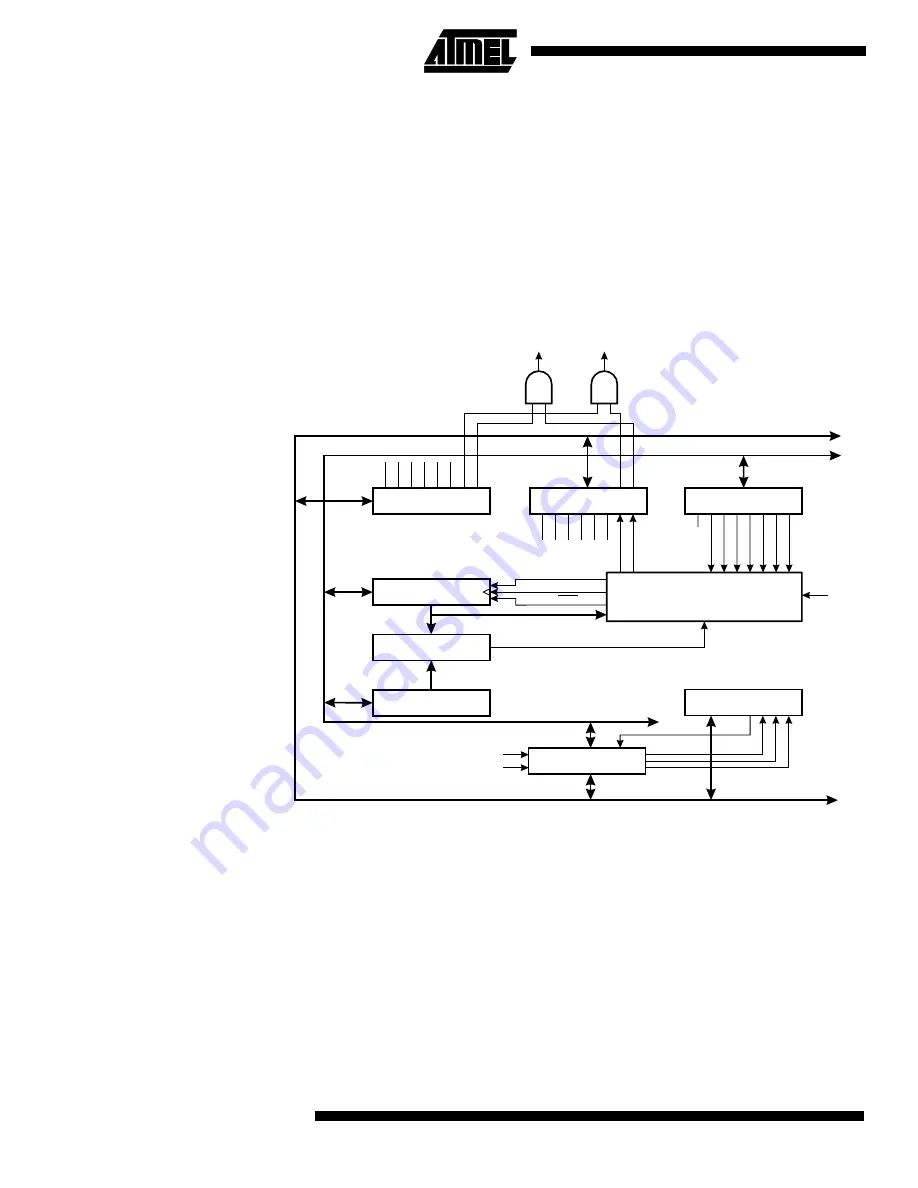

Figure 30 shows the block diagram for Timer/Counter0. Figure 31 shows the block dia-

gram for Timer/Counter2.

Figure 30.

Timer/Counter0 Block Diagram

8-BIT DATA BUS

8-BIT ASYNCH T/C0 DATA BUS

ASYNCH. STATUS

REGISTER (ASSR)

TIMER INT. FLAG

REGISTER (TIFR)

TIMER/COUNTER0

(TCNT0)

SYNCH UNIT

8-BIT COMPARATOR

OUTPUT COMPARE

REGISTER0 (OCR0)

TIMER INT. MASK

REGISTER (TIMSK)

0

0

0

7

7

7

T/C CLK SOURCE

UP/DOWN

T/C CLEAR

CONTROL

LOGIC

OCF0

TO

V

0

TO

V

1

OCF2A

OCF2B

ICF1

TO

V

2

OCF2

OCF0

TO

V

0

OCIE0

T

OIE0

T

OIE1

OCIE1A

OCIE1B

TICIE1

T

OIE2

OCIE2

OCR0UB

TC0UB

ICR0UB

PCK0

CK

TCK0

T/C0 OVER-

FLOW IRQ

T/C0 COMPARE

MATCH IRQ

T/C0 CONTROL

REGISTER (TCCR0)

CS02

COM01

PWM0

AS0

CS01

COM00

CS00

CTC0