126

ATmega103(L)

0945G–09/01

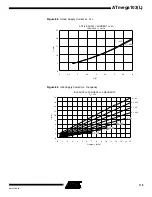

Figure 96.

I/O Pin Source Current vs. Output Voltage

Figure 97.

I/O Pin Sink Current vs. Output Voltage

0

2

4

6

8

10

12

14

16

18

20

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

I/O PIN SOURCE CURRENT vs. OUTPUT VOLTAGE

V = 5V

cc

I

(mA)

OH

V (V)

OH

T = 85

˚

C

A

T = 25

˚

C

A

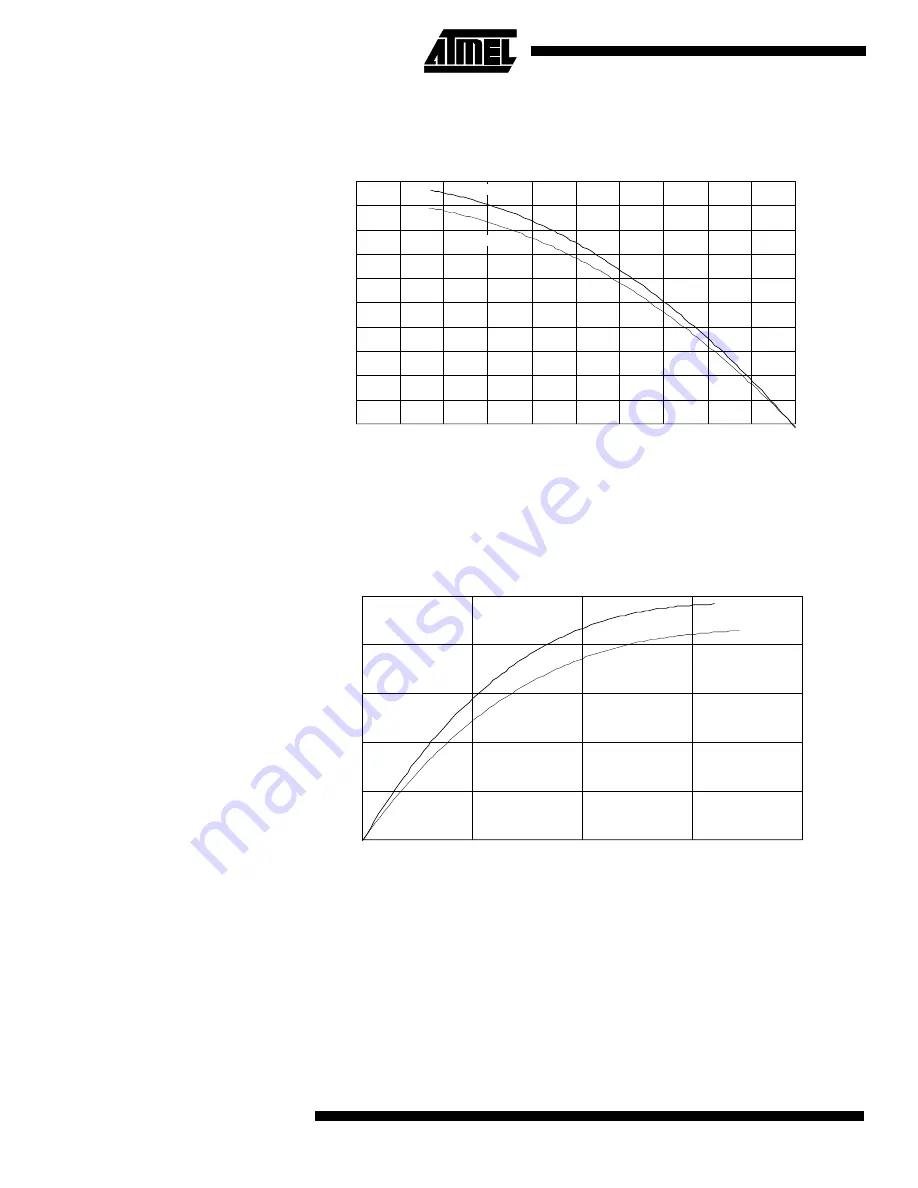

0

5

10

15

20

25

0

0.5

1

1.5

2

I

(mA)

OL

V (V)

OL

T = 85

˚

C

A

T = 25

˚

C

A

I/O PIN SINK CURRENT vs. OUTPUT VOLTAGE

V = 2.7V

cc