S1C63656 TECHNICAL MANUAL

EPSON

93

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Serial Interface)

ESOUT: SOUT enable register (FF70H•D2)

Enables serial data output from the P11 port.

When "1" is written: Enabled (SOUT)

When "0" is written: Disabled (I/O port)

Reading: Valid

When serial data output is not used, the SOUT output can be disabled to use P11 as an I/O port. When

performing serial output, write "1" to ESOUT to set P11 as the SOUT output port.

At initial reset, this register is set to "0".

PUL10: SIN (P10) pull-down control register (FF45H•D0)

PUL12: SCLK (P12) pull-down control register (FF45H•D2)

Sets the pull-down of the SIN terminal and the SCLK terminals (in the slave mode).

When "1" is written: Pull-down On

When "0" is written: Pull-down Off

Reading: Valid

Enables or disables the pull-down resistor built into the SIN (P10) and SCLK (P12) terminals. (Pull-down

resistor is only built in the port selected by mask option.)

SCLK pull-down is effective only in the slave mode. In the master mode, the PUL12 register can be used

as a general purpose register.

At initial reset, these registers are set to "1" and pull-down goes on.

SCS0, SCS1: Clock mode selection register (FF71H•D0, D1)

Selects the synchronous clock (SCLK) for the serial interface.

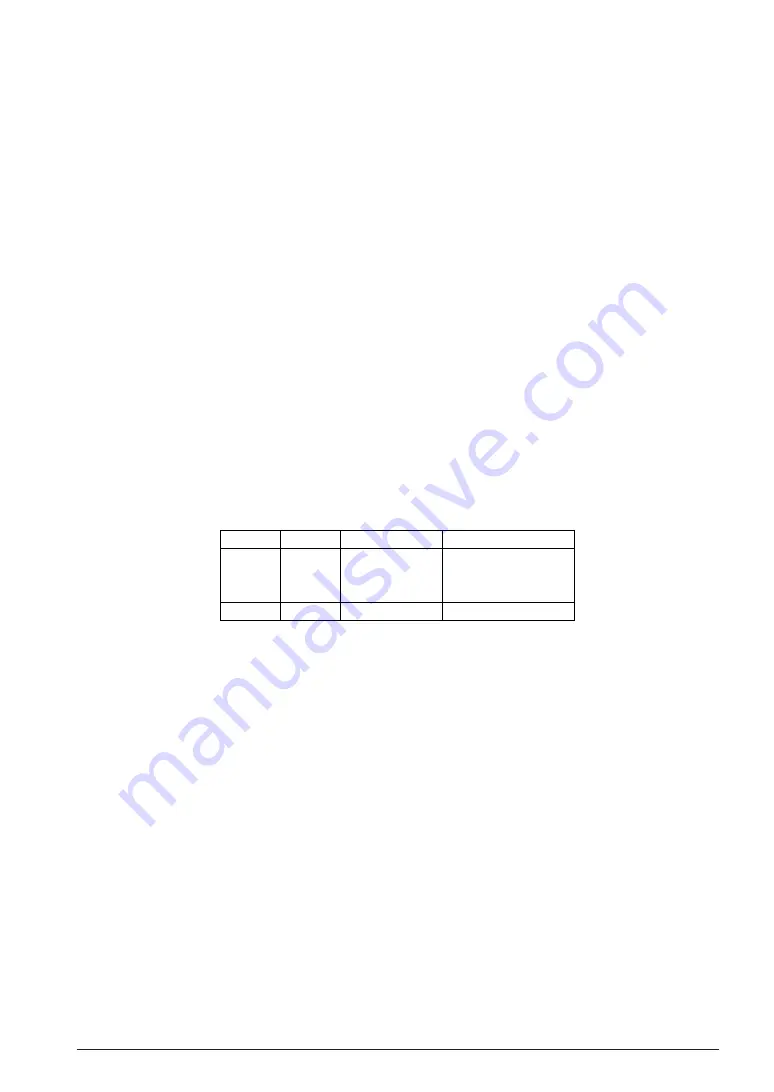

Table 4.11.5.2 Synchronous clock selection

SCS1

1

1

0

0

SCS0

1

0

1

0

Mode

Master mode

Slave mode

Synchronous clock

OSC1

OSC1 /2

Programmable timer

∗

External clock

∗

∗

The maximum clock is limited to 1 MHz.

Synchronous clock (SCLK) is selected from among the above 4 types: 3 types of internal clock and

external clock.

When the programmable timer is selected, the signal that is generated by dividing the underflow signal

of the programmable timer (timer 1) in 1/2 is used as the synchronous clock. In this case, the program-

mable timer must be controlled before operating the serial interface. Refer to Section 4.10, "Programmable

Timer" for the control of the programmable timer.

At initial reset, external clock is selected.

SCPS: Clock phase selection register (FF71H•D2)

Selects the timing for reading in the serial data input from the SIN (P10) terminal.

• When positive polarity is selected:

When "1" is written: Rising edge of SCLK

When "0" is written: Falling edge of SCLK

Reading: Valid

• When negative polarity is selected:

When "1" is written:

_________

Falling edge of SCLK

When "0" is written:

_________

Rising edge of SCLK

Reading: Valid

Select whether the fetching for the serial input data to registers (SD0–SD7) at the rising edge or falling

edge of the synchronous signal.