72

EPSON

S1C63656 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Programmable Timer)

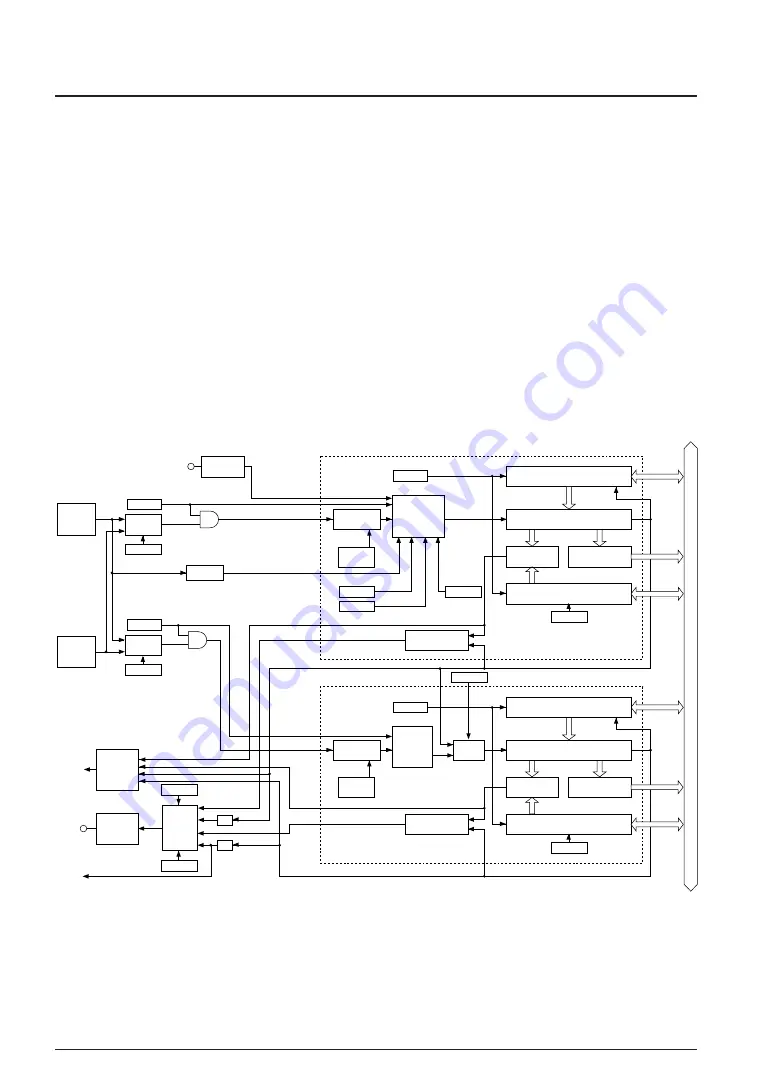

4.10 Programmable Timer

4.10.1 Configuration of programmable timer

The S1C63656 has two 8-bit programmable timer systems (timer 0 and timer 1) built-in.

The timers are composed of 8-bit presettable down counters and they can be used as 8 bits

×

2 channels or

16 bits

×

1 channel of programmable timers. Timer 0 also has an event counter function using the K13

input port terminal.

Figure 4.10.1.1 shows the configuration of the programmable timer.

Each timer has an 8-bit down counter and an 8-bit reload data register. The down counter counts the

input clock. When the down counter underflows, the timer outputs the underflow and interrupt signals

and resets the counter to its initial value. The reload data register is used to store that initial value. The

underflow signal of timer 1 is used as the source clock of the serial interface, this makes it possible to

program a flexible transfer rate.

Each timer has an 8-bit compare data register in addition to the above registers. This register is used to

store data to be compared with the contents of the down counter. When the timer is set in the PWM

mode, the timer outputs the compare match signal if the contents between the down counter and the

compare data register are matched, and an interrupt occurs at the same time. Also the compare match

signal is used with the underflow signal to generate a PWM waveform.

The signal generated by the programmable timer can be output from the R02 output port terminal.

Interrupt

request

CHSEL0

TOUT

(R02)

Serial

interface

Interrupt

control

circuit

PTOUT

Selector

Output port

R02

1/2

1/2

Reload data register

RLD00–RLD07

Data buffer

PTD00–PTD07

PWM waveform

generator

Compare data register

CD00–CD07

PTRUN0

Timer 0

PTPS00

PTPS01

8-bit

down counter

Prescaler

Selector

CKSEL0

Timer 0 Run/Stop

Clock

control

circuit

Prescaler

setting

Under-

flow

signal

Compare

match

signal

Compare

match

signal

Data bus

Selector

CKSEL1

PTSEL0

MOD16

Timer 1 Run/Stop

PTRST0

Timer 0 reset

PWM output selection

2,048 Hz

Divider

OSC3

oscillation

circuit

OSC1

oscillation

circuit

f

OSC3

f

OSC1

PWM waveform

generator

Data buffer

PTD10–PTD17

Comparator

Comparator

Compare data register

CD10–CD17

PTSEL1

PWM output selection

Timer 1

PTPS10

PTPS11

8-bit

down counter

Prescaler

Selector

Clock

control

circuit

Prescaler

setting

Under-

flow

signal

PTRST1

Timer 1 reset

16-bit mode selection

Reload data register

RLD10–RLD17

PTRUN1

Input port

K13

K13

FCSEL

PLPOL

Timer function setting

Pulse polarity setting

EVCNT

Event counter

mode setting

Fig. 4.10.1.1 Configuration of programmable timer