S1R72104 Technical Manual

16

EPSON

Rev.1.1

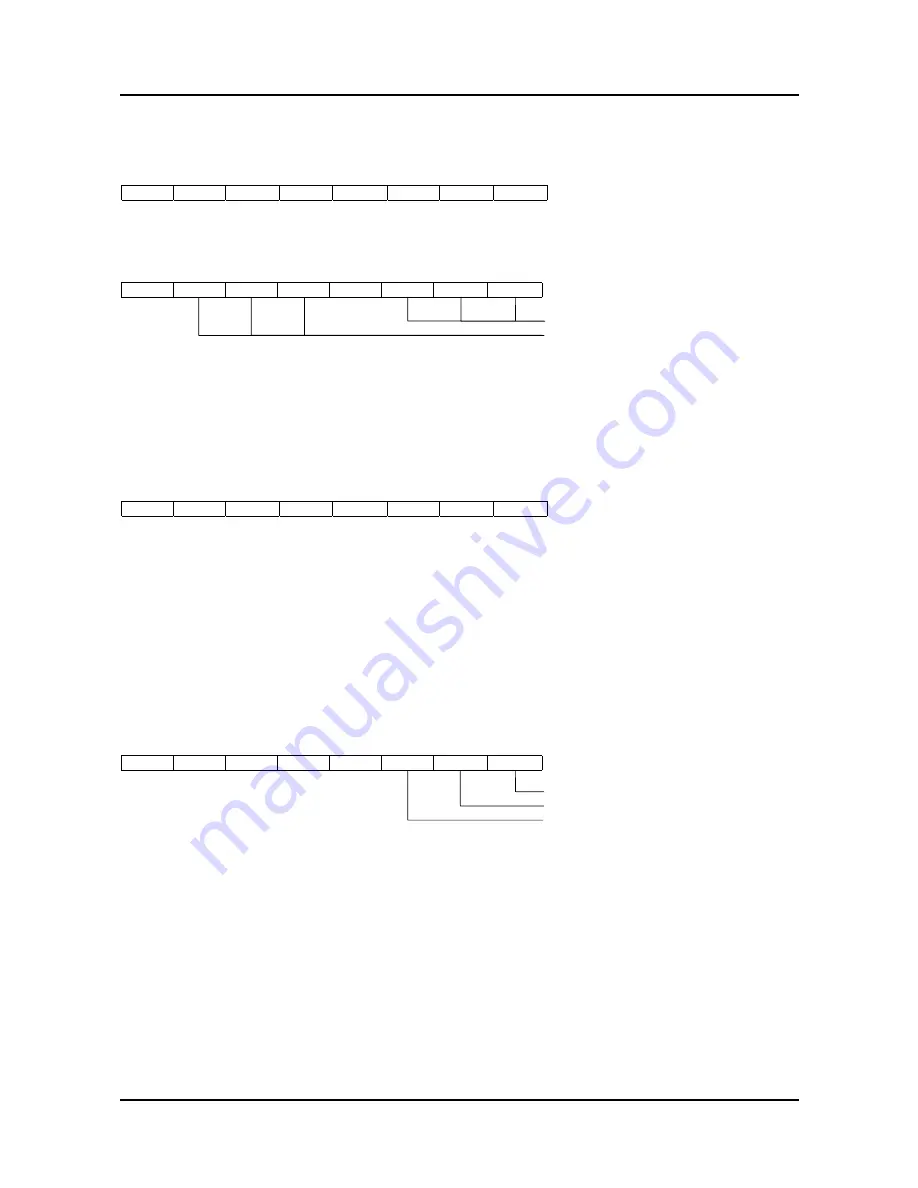

7.3.10 SCSI Own ID (OWNID) R/W

Sets the SCSI-ID of this IC itself.

7 6 5 4 3 2 1 0

- -

-

-

-

OID2 OID2 OID0

0Eh

7.3.11 Source/Destination ID (SDID) R/W

Sets both the SCSI-ID of the selector side and the target SCSI-ID when selection is made.

7 6 5 4 3 2 1 0

- SID2 SID1 SID0 -

DID2

DID1 DID0

0Fh

DESTINATION

ID

(R)

SOURCE

ID

(R/W)

In Initiator mode, sets the target SCSI-ID to be selected in DESTINATION ID.

When re-selection is received, the target SCSI-ID which made re-selection is set in SOURCE ID.

In Target mode, sets the initiator SCSI-ID to be re-selected in DESTINATION ID.

When selection is received, the initiator SCSI-ID which made selection is set in SOURCE ID.

7.3.12 Selection Timeout Counter (SLTIME) R/W

Sets time-out delay for selection and re-selection.

7 6 5 4 3 2 1 0

ST7

ST6 ST5 ST4 ST3

ST2 ST1 ST0

10h

The time-out delay value is calculated according to the following formula:

Delay value = count value

×

2

15

×

T

×

2

Where, T is internal clock cycle (40MHz).

The IC acts as follows if it detected time-out:

Suspends to output ID bit.

Negates XSSEL 4000

×

T

×

2 (about 200µs) after such suspension, and outputs selection time-out interrupt.

No time-out is detected if “0” is set to this register.

7.3.13 FIFO Control (FIFOCTL) R/W

Used for clearing the data of SCSI-FIFO and for checking its status.

7 6 5 4 3 2 1 0

- -

-

- - FCLR

FULL

EMPTY

11h

FIFO EMPTY

FIFO

FULL

CLEAR FIFO

BIT7,6,5,4,3 RESERVED

BIT2 CLEAR FIFO

HIGH of this bit clears the data stored in SCSI-FIFO.

The bit returns to LOW automatically after such clearing.

BIT1 FULL

HIGH of this bit means that SCSI-FIFO is full. In such a condition, any data written in SCSI-FIFO is ignored.

BIT0 EMPTY

HIGH of this bit means that SCSI-FIFO is empty. In such a condition, any trial to read data from SCSI-FIFO results

in invalid data read out.