Semiconductor Group

4-83

1998-04-01

Instruction Set

C500 Family

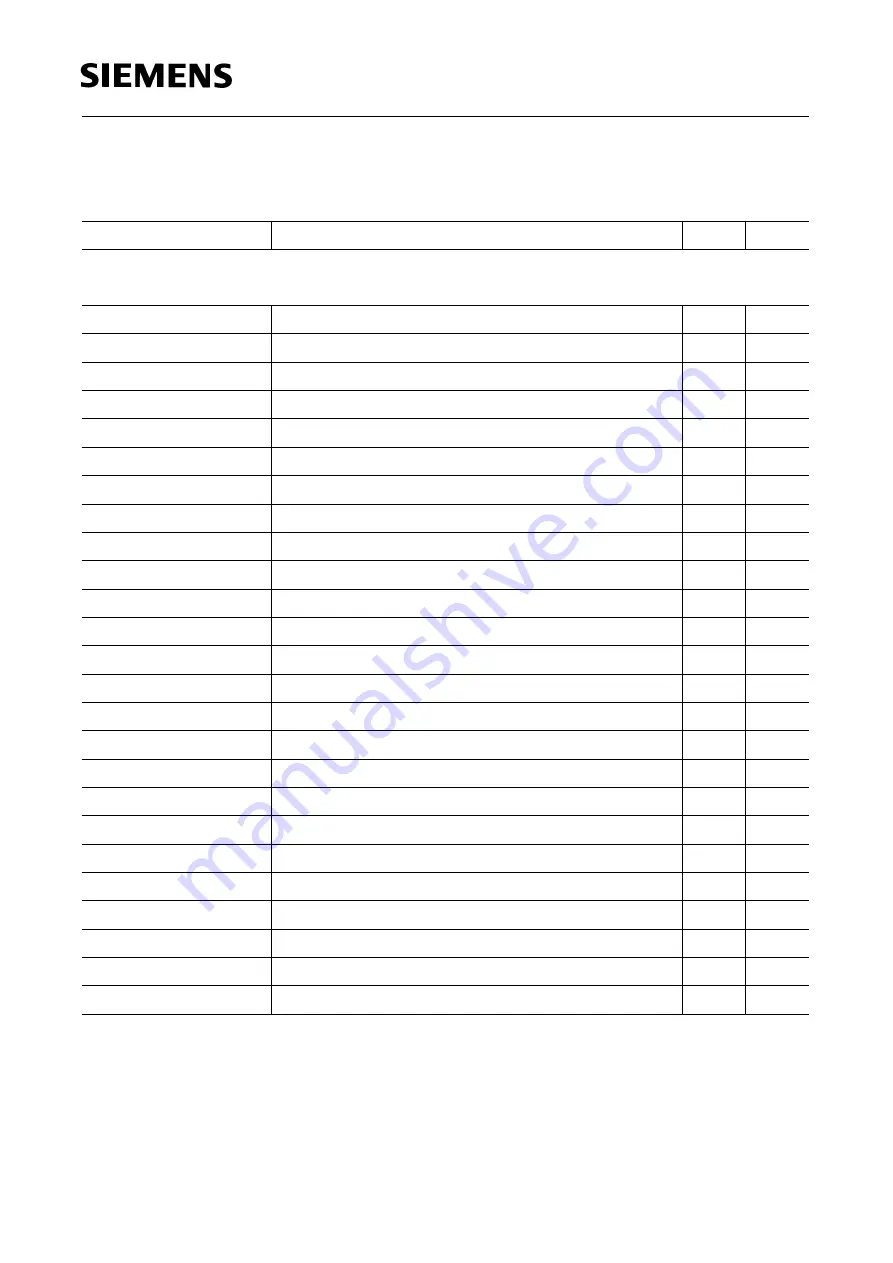

Logic Operations

ANL

A,Rn

AND register to accumulator

1

1

ANL

A,direct

AND direct byte to accumulator

2

1

ANL

A,@Ri

AND indirect RAM to accumulator

1

1

ANL

A,#data

AND immediate data to accumulator

2

1

ANL

direct,A

AND accumulator to direct byte

2

1

ANL

direct,#data

AND immediate data to direct byte

3

2

ORL

A,Rn

OR register to accumulator

1

1

ORL

A,direct

OR direct byte to accumulator

2

1

ORL

A,@Ri

OR indirect RAM to accumulator

1

1

ORL

A,#data

OR immediate data to accumulator

2

1

ORL

direct,A

OR accumulator to direct byte

2

1

ORL

direct,#data

OR immediate data to direct byte

3

2

XRL

A,Rn

Exclusive OR register to accumulator

1

1

XRL

A direct

Exclusive OR direct byte to accumulator

2

1

XRL

A,@Ri

Exclusive OR indirect RAM to accumulator

1

1

XRL

A,#data

Exclusive OR immediate data to accumulator

2

1

XRL

direct,A

Exclusive OR accumulator to direct byte

2

1

XRL

direct,#data

Exclusive OR immediate data to direct byte

3

2

CLR

A

Clear accumulator

1

1

CPL

A

Complement accumulator

1

1

RL

A

Rotate accumulator left

1

1

RLC

A

Rotate accumulator left through carry

1

1

RR

A

Rotate accumulator right

1

1

RRC

A

Rotate accumulator right through carry

1

1

SWAP A

Swap nibbles within the accumulator

1

1

Table 4-3 :

Instruction Set Summary (contÕd)

Mnemonic

Description

Byte

Cycle