CPU Timing

C500 Family

Semiconductor Group

3-3

1998-04-01

3.2

Accessing External Memory

There are two types of external memory accesses: accesses to external program memory and

accesses to external data memory. Accesses to external program memory use the signal PSEN

(program store enable) as the read strobe. Accesses to external data memory use the RD or WR

(alternate functions of P3.7 and P3.6) to access the memory.

Fetches from external program memory always use a 16-bit address. Accesses to external data

memory can use either a 16-bit address (MOVX @DPTR) or an 8-bit address (MOVX @Ri).

Whenever a 16-bit address is used, the high byte of the address comes out on port 2, where it is

held for the duration of the read, write, or code fetch cycle.

If an 8-bit address is being used (MOVX @Ri), the contents of the port 2 SFR remain at the port 2

pins throughout the whole external memory cycle. In this case, port 2 pins can be used to page the

external data memory.

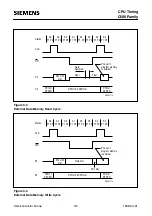

In either case, the low byte of the address is time-multiplexed with the data byte on port 0. The

ADDRESS/DATA signal drives both FETS in the port 0 output buffers. Thus, in external bus mode

the port 0 pins are not open-drain outputs and do not require external pullups. The ALE (address

latch enable) signal should be used to latch the address byte into an external latch. The address

byte is valid at the negative transition of ALE. Then, in a write cycle, the data byte to be written

appears on port 0 just before WR is activated, and remains there until WR is deactivated. In a read

cycle, the incoming byte is accepted at port 0 just before the read strobe (RD) is deactivated.

During any access to external memory, the CPU writes FFH to the port 0 latch (the special function

register), thus obliterating the information in the port 0 SFR. Also, a MOV P0 instruction must not

take place during external memory accesses. If the user writes to port 0 during an external memory

fetch, the incoming code byte may be corrupted. Therefore, do not write to port 0 if external memory

is used.

3.2.1 Accessing External Program Memory

External program memory is accessed under two conditions:

1. Whenever signal EA is active (low), or

2. Whenever signal EA is inactive (high) and the program counter (PC) contains an address greater

than the internal ROM size (e.g. 1FFFFH for an 8K internal ROM or 3FFFH for an 16K internal

ROM).

This requires that the ROMless versions have always EA wired to Vss to enable the lower 8K, 16K,

or 32K program bytes to be fetched from external memory.

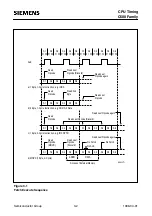

When the CPU is executing out from external program memory (see timing diagram in

),

all 8 bits of port 2 are dedicated to an output function and may not be used for general purpose I/O.

During external program fetches they output the high byte of the PC with the port 2 drivers using the

strong pullups to emit bits that are 1«s.