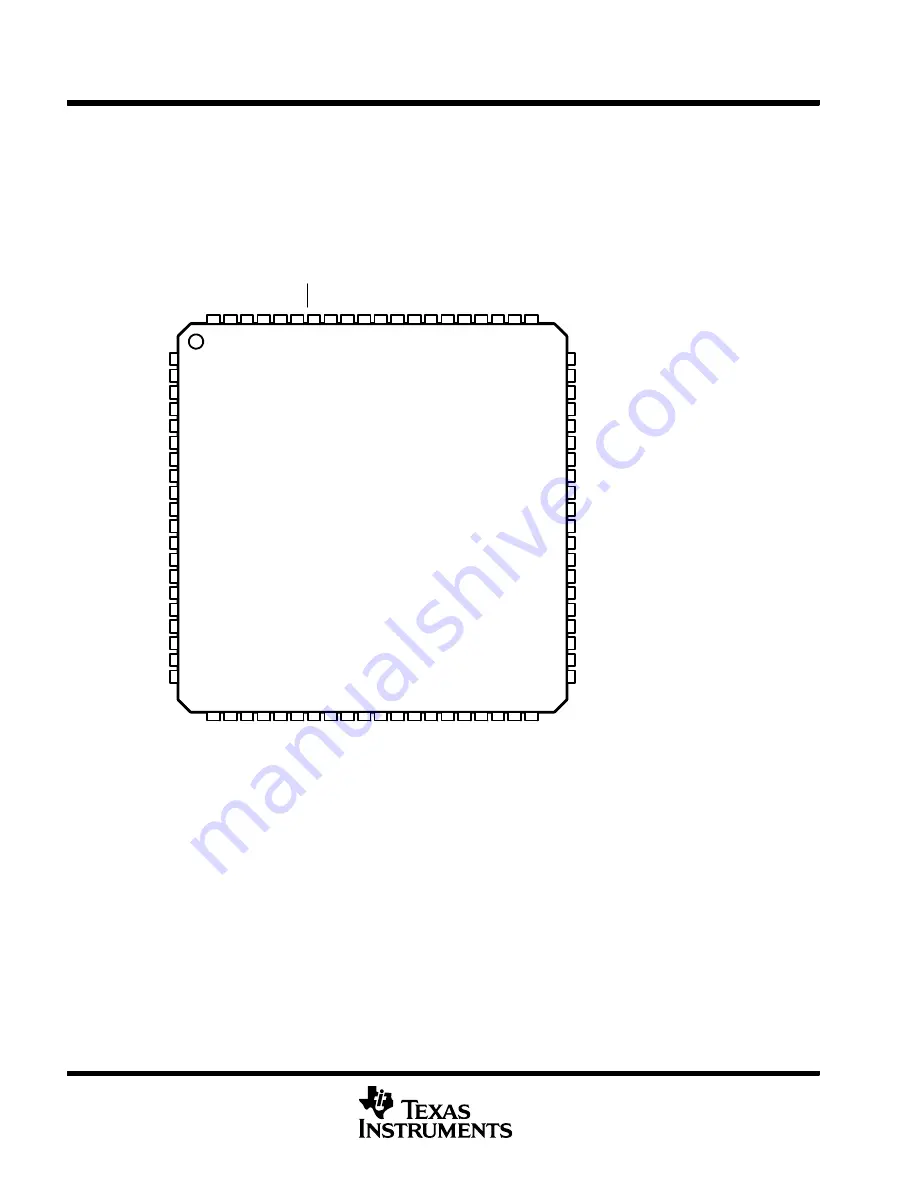

MSP430FG47x

MIXED SIGNAL MICROCONTROLLER

SLAS580D -- OCTOBER 2008 -- REVISED MARCH 2011

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

pin designation, MSP430FG47xIPN

80-pin

IPN PACKAGE

(TOP VIEW)

DV

CC1

60

59

80 79

P6.3/

A1+

/O

A1O

P6.4/

A1-

/O

A1F

B

P6

.5/

O

A0

I2

(

S

W0

B)

P6

.6/

O

A1

I1

(

S

W1

A)

P6.7/OA1I2/SVSIN (SW1B)

XIN

XOUT

V

REF

GND

P2.6/CAOUT/S2

P2.7/S3

P4.7/S4

P4.6/S5

P4.5/S6

P4.0/S11

S12

S13

S1

4

S1

5

S1

7

S1

8

S1

9

P5

.0

/S20

P5

.1

/S21

S2

2

P3.2/UCB0SOMI/UCB0SCL/S27

P3.1/UCB0SIMO/UCB0SDA/S26

P3.0/UCB0STE/UCA0CLK

P5

.7/

R

0

3

DV

CC

2

DV

SS

1

DV

SS2

P

6.2/

O

A

0I1

(

S

W0A)

P6.1/

A0-

/O

A0F

B

P6.0/

A0+

/O

A0O

RS

T/

NM

I

TCK

TMS

T

D

I/T

CLK

TDO

/TD

I

P

5.6

/LCD

REF

/R

1

3

78 77 76 75 74 73 72 71 70 69 68 67 66 65

58

57

56

55

54

53

52

51

50

49

48

47

46

45

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36

64 63 62 61

37

S2

3

38 39 40

44

43

42

41

P4.4/S7

P4.3/S8

P4.2/S9

P4.1/S10

17

18

19

20

P3.7/S31

P3.6/S30

P3.5/S29

P3.4/S28

P3.3/UCB0CLK/UCA0STE

S2

4

S2

5

COM

0

P5.

2/COM

1

P5.

3/COM

2

P5.

4/COM

3

P2.5/

U

C

A

0R

XD

/U

CA0

S

OM

I

P

2.

4/

U

CA0

T

X

D

/UCA

0S

IM

O

P2

.3/

T

B2

P2.2/TB1

P2.1/TB0/S0

P2.0/TA2/S1

P1.7/CA1/A2+

P1.6/CA0/A2-/OA0I0/DAC0

P1.5/TACLK/ACLK/A3+

P1.4/TBCLK/SMCLK/A3-/OA1I0/DAC1

P1.3/TBOUTH/SVSOUT/A4+/OA1I3 (SW1C)

P1.2/TA1/A4-/OA0I3 (SW0C)

P1.1/TA0/MCLK/OA1RFB

P1.0/TA0/OA0RFB

AV

CC

AV

SS

LCDCA

P

/R

3

3

P5

.5/

R

2

3

XT

2O

U

T

XT

2I

N

S1

6

GND

Summary of Contents for MSP430FG47x

Page 91: ......