CPU Description

Program Status Word (PSW) [FL]

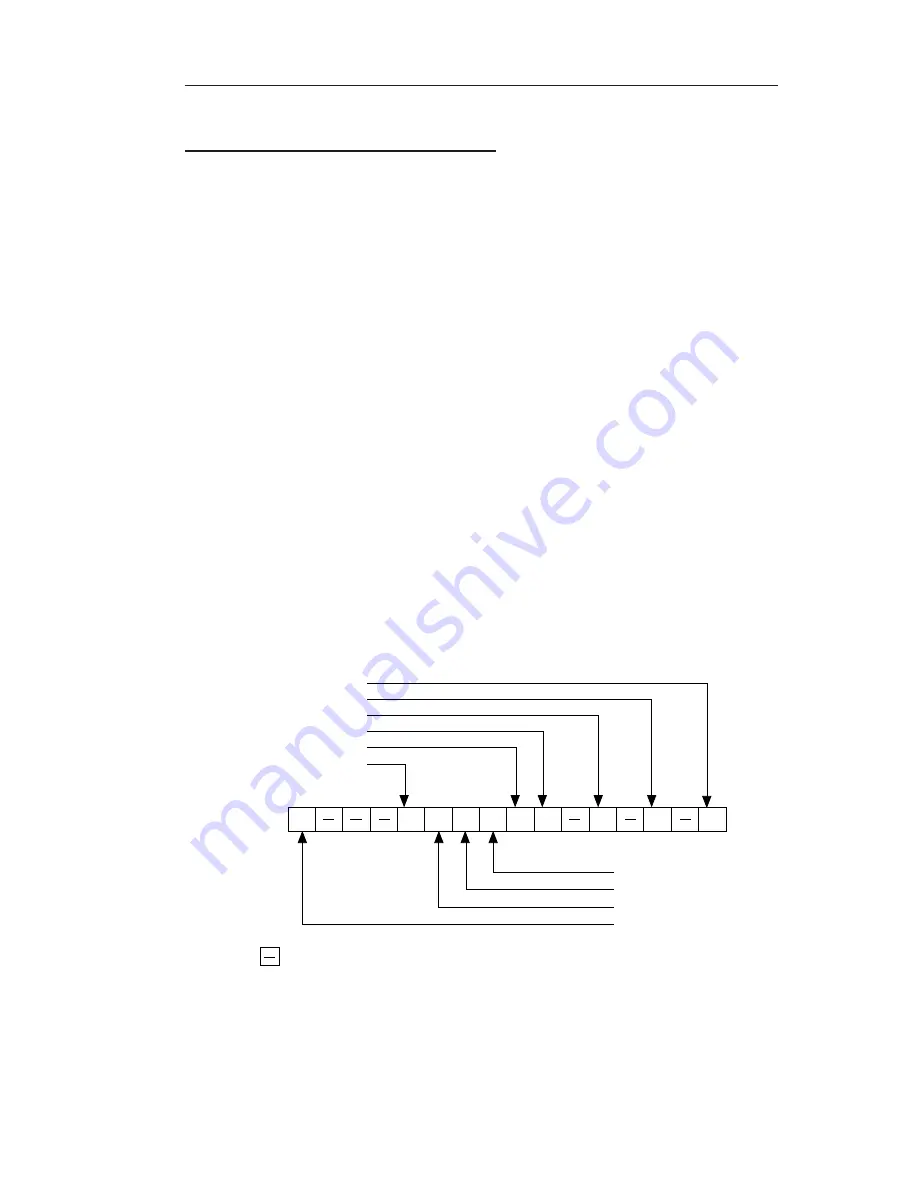

The program status word is a 16-bit register containing status and

control flag information important to CPU and program operation.

There are six status flags and four control flags whose bits are defined

in Figure 6-1. Notice that some of the bits are not defined, but are

reserved for future processor designs.

The status flags provide information about the result of the previous

arithmetic or logical processor operation. The status flags are set to

logical 1 or reset to logical 0 by the EXU based on the result of the

previous operation. These flags are generally tested by conditional

jump and branch instructions to affect program execution.

The control flags are used by the programmer to direct CPU

operation. They are set to logical 1 or reset to logical 0 by specific

processor instructions. The interrupt enable (IE) [IF] and break

(BRK) [TF] flags are automatically reset upon entering an interrupt

service routine. Refer to a V20 or an 8088 Assembly Programmer’s

Reference manual for descriptions of the instructions and how they

affect each of the control and status flags.

15

14

13

12

11 10

9

8

7

6

5

4

3

2

1

0

MD

V

(OF)

DIR

(DF)

IE

(IF)

BRK

(TF)

S

(SF)

Z

(ZF)

AC

(AF)

P

(PF)

CY

(CF)

CONTROL FLAGS:

BREAK

INTERRUPT ENABLE

DIRECTION

MODE

STATUS

WORD:

STATUS FLAGS:

CARRY

PARITY

AUXILIARY CARRY

ZERO

SIGN

OVERFLOW

RESERVED

Figure 6–1. Program Status Word.

6-8