A96G140/A96G148/A96A148 User’s manual

12. Timer 0/1/2/3/4/5

121

12.4

Timer 3

A 16-bit timer 3 consists of a multiplexer, timer 3 A data high/low register, timer 3 B data high/low

register and timer 3 control high/low register (T3ADRH, T3ADRL, T3BDRH, T3BDRL, T3CRH, and

T3CRL).

Timer 3 operates in one of the following modes:

16-bit timer/counter mode

16-bit capture mode

16-bit PPG output mode (one-shot mode)

16-bit PPG output mode (repeat mode)

The timer/counter 3 can be clocked by an internal or an external clock source (EC3). The clock source

is selected by a clock selection logic controlled by clock selection bits (T3CK[2:0]).

TIMER 3 clock source: fX/1, fX/2, fX/4,fX/8,fX/64, fX/512, fX/2048 and EC3

In capture mode, data is captured into input capture data registers (T3BDRH/T3BDRL) by EINT3. Timer

3 results in the comparison between counter and data register through T3O port in timer/counter mode.

In addition, timer 3 outputs PWM waveform through PWM3O port in the PPG mode.

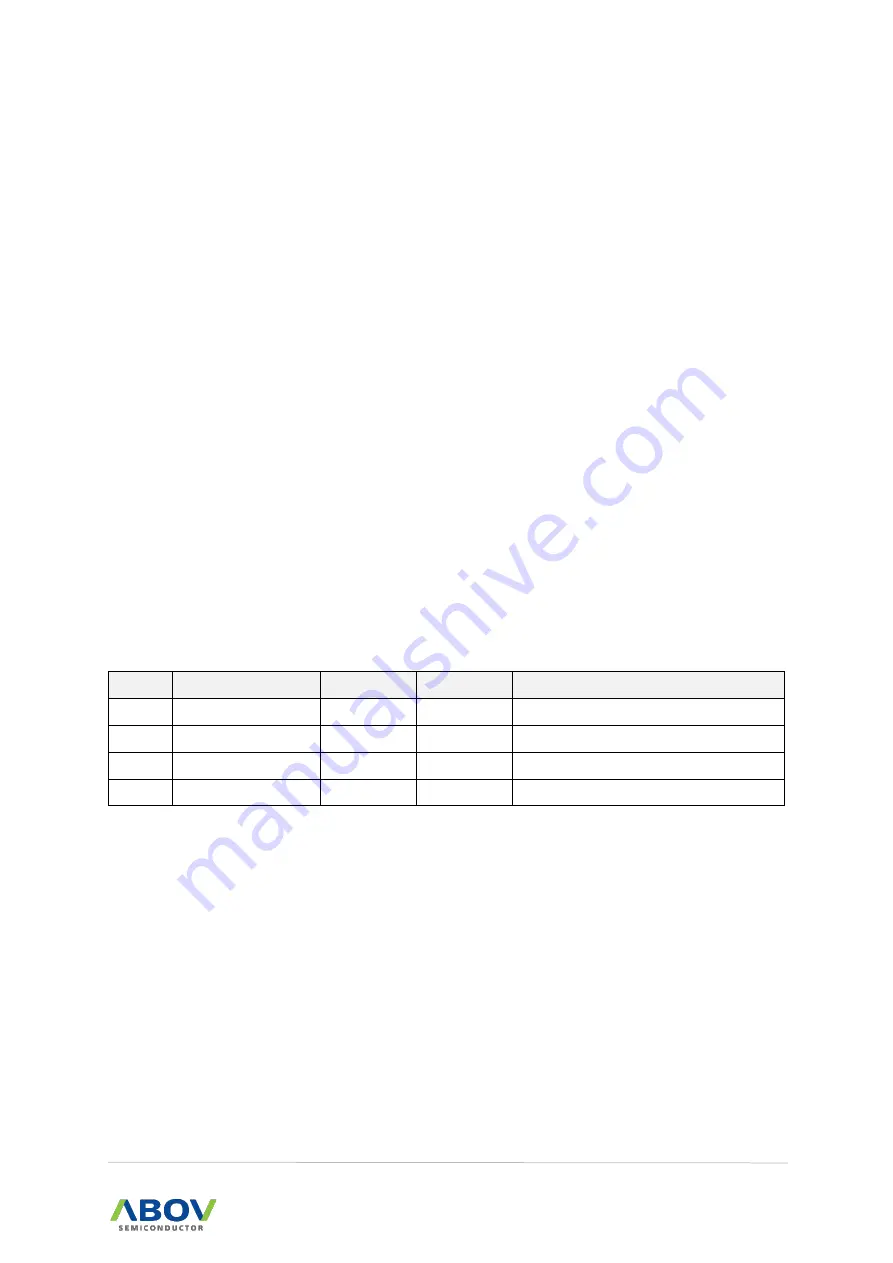

Table 20. TIMER 3 Operating Modes

T3EN

P0FSRH[1:0]

T3MS[1:0]

T3CK[2:0]

Timer 3

1

11

00

XXX

16 Bit Timer/Counter Mode

1

00

01

XXX

16 Bit Capture Mode

1

11

10

XXX

16 Bit PPG Mode(one-shot mode)

1

11

11

XXX

16 Bit PPG Mode(repeat mode)

12.4.1

16-bit timer/counter mode

16-bit timer/counter mode is selected by control registers, and the 16-bit timer/counter has counter

registers and data registers as shown in figure 52. The counter register is increased by internal or

external clock input. Timer 3 can use the input clock with one of 1, 2, 4, 8, 64, 512 and 2048 prescaler

division rates (T3CK[2:0]). When the values of T3CNTH/T3CNTL and T3ADRH/T3ADRL are identical

to each other in timer 3, a match signal is generated and the interrupt of Timer 3 occurs. The

T3CNTH/T3CNTL values are automatically cleared by the match signal. It can be cleared by software

(T3CC) too.

External clock (EC3) counts up the timer at the rising edge. If the EC3 is selected as a clock source by

T3CK[2:0], EC3 port should be set as an input port by configuring P00 IO bit.