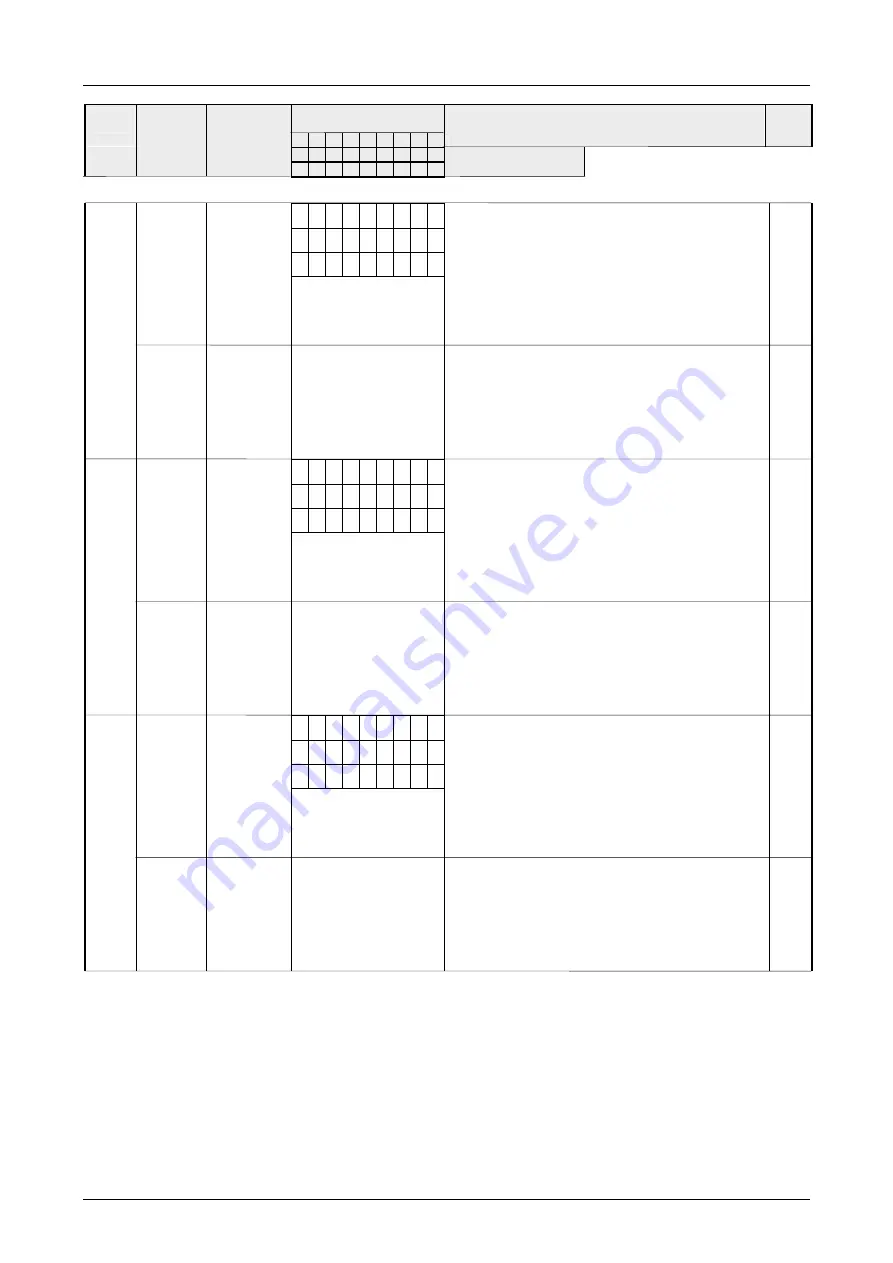

Chapter 9 Instruction list

CPU ADAM 821x

Command

Operand

Parameter

Status word

Function

Length

in

BR

CC1 CC0 OV OS OR STA RLO /FC

words

: Instruction depends on

: Instruction influences

8-28

ADAM 8000 Manual CPU 821x – Rev 1.1

ON

BR

CC1 CC0 OV OS OR STA RLO /FC

OR operation at signal state "0"

I/Q

a.b 0.0 ... 127.7

- - - - - - - Y Y Input/output

1/2

M

a.b 0.0 ... 1023.7 - - - - - 0 Y Y 1 Bit memory

1/2

L

a.b 0.0 ... 1043.7

Local data bit

2

DBX

a.b 0.0 ... 8191.7

Data bit

2

DIX

a.b 0.0 ... 8191.7

Instance data bit

2

c

[AR1,m]

register-indirect, area-internal (AR1)

2

c

[AR2,m]

register-indirect, area-internal (AR2)

2

[AR1,m]

area-crossing (AR1)

2

[AR2,m]

area-crossing (AR2)

2

Parameter

via parameters

2

X

BR

CC1 CC0 OV OS OR STA RLO /FC

EXCLUSIVE-OR operation at signal state "1"

I/Q

a.b 0.0 ... 127.7

- - - - - - - Y Y Input/output

2

M

a.b 0.0 ... 1023.7 - - - - - 0 Y Y 1 Bit memory

2

L

a.b 0.0 ... 1043.7

Local data bit

2

DBX

a.b 0.0 ... 8191.7

data bit

2

DIX

a.b 0.0 ... 8191.7

Instance data bit

2

c

[AR1,m]

register-indirect, area-internal (AR1)

2

c

[AR2,m]

register-indirect, area-internal (AR2)

2

[AR1,m]

area-crossing (AR1)

2

[AR2,m]

area-crossing (AR2)

2

Parameter

via parameters

2

XN

BR

CC1 CC0 OV OS OR STA RLO /FC

EXCLUSIVE-OR operation at signal state "0"

I/Q

a.b 0.0 ... 127.7

- - - - - - - Y Y Input/output

2

M

a.b 0.0 ... 1023.7 - - - - - 0 Y Y 1 Bit memory

2

L

a.b 0.0 ... 1043.7

Local data bit

2

DBX

a.b 0.0 ... 8191.7

Data bit

2

DIX

a.b 0.0 ... 8191.7

Instance data bit

2

c

[AR1,m]

register-indirect, area-internal (AR1)

2

c

[AR2,m]

register-indirect, area-internal (AR2)

2

[AR1,m]

area-crossing (AR1)

2

[AR2,m]

area-crossing (AR2)

2

Parameter

via parameters

2