13

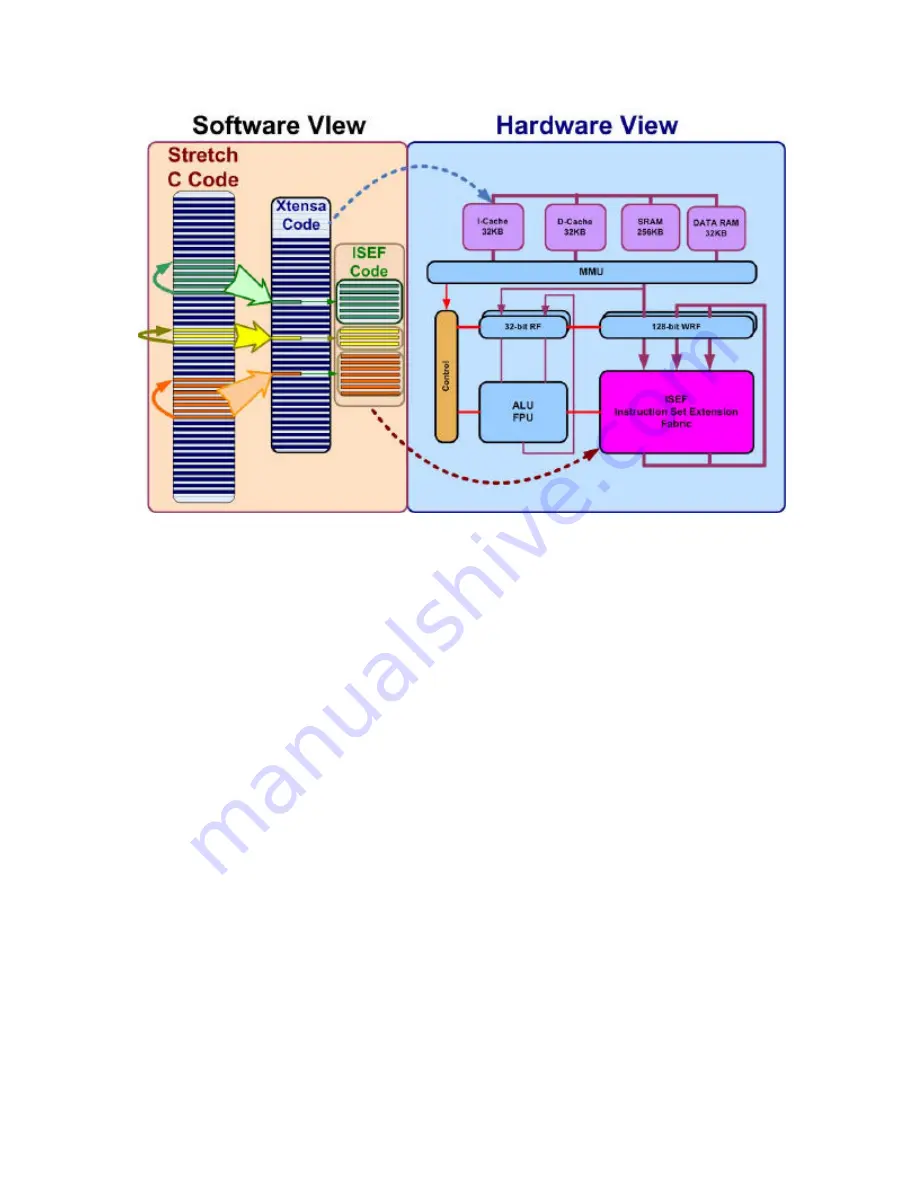

Figure 4 –C kernels transformed into Stretch ISEF Extended Instructions

Using C programming language to implement data-parallel computations in the ISEF unit

concurrently with Xtensa ISA is a very useful feature that is very effective in the DSP and ISP-

type data-intensive applications.

Memory System

The SCP memory architecture is designed to support multiple simultaneous data transfers to

various internal functional devices. It includes:

?

256KB on-chip single-port SRAM

?

32KB dual-port data SRAM

?

32KB Data cache

?

32KB Instruction cache

?

DDR SDRAM controller to up to 3GB of external SDRAM

The SCP DDR SDRAM controller interfaces to the various available DDR400 memories. It

supports the following features:

?

Clock frequencies from 100 to 200 MHz

?

Fully pipelined command, read, and write data interface

?

Advanced bank look-ahead for high memory throughput

SysAD Interface

The SysAD bus interface allows the SCP to be a co-processor to the front-end FPGA with the

FPGA using DMA data transfers directly in the SCP memory. The FPGA operations are