Functional Description

2-6

Copyright © 2002, 2003 ARM Limited. All rights reserved.

ARM DDI 0275D

2.3

Control logic

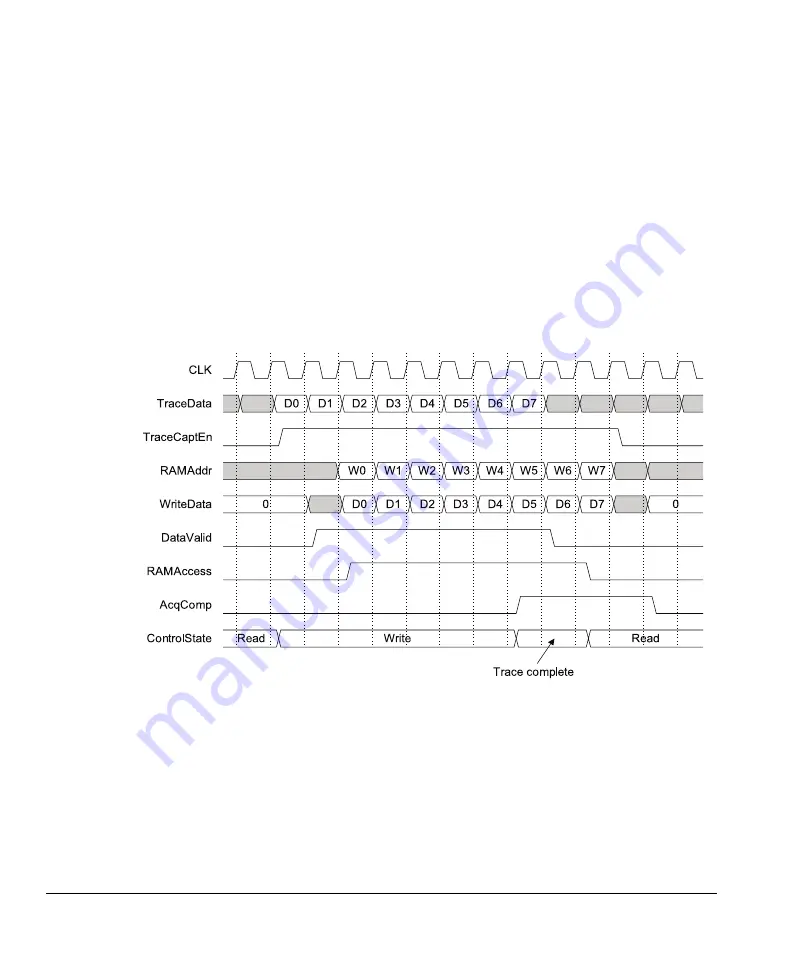

Control logic monitors the

TraceCaptEn

signal, the status flags, and the

DataValid

signal from the Data Formatter. The logic enables a RAM write access cycle when there

is valid data and trace capture is active. Trace capture is active while the

TraceCaptEn

signal is asserted and

TrgDelayCounter

is nonzero.

TraceCaptEn

directly selects RAM write or read mode and the RAM address source.

When

TraceCaptEn

is asserted all RAM access cycles are writes using the write

pointer as the address. When

TraceCaptEn

is deasserted, RAM accesses are controlled

by the AHB interface when

SoftwareCntl

(control register bit 4) is HIGH and

SWEN

is HIGH. Otherwise, all access cycles are reads using the RAM Read Pointer Register

as the address. Timing diagrams showing the operation of the control logic are given in

Figure 2-2 and Figure 2-3 on page 2-7.

Figure 2-2 Trace capture operation

Summary of Contents for ETB11

Page 6: ...List of Tables vi Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 8: ...List of Figures viii Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 46: ...Functional Description 2 26 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 70: ...Signal Descriptions A 6 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 78: ...Glossary Glossary 4 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...