Functional Description

2-22

Copyright © 2002, 2003 ARM Limited. All rights reserved.

ARM DDI 0275D

Synchronous HCLK and CLK

When

HCLK

and

CLK

are synchronous,

HCLKEN

is used to control the generation

of

HCLK

, which is derived from

CLK

. This means that the

HCLK

rising edge always

corresponds to a

CLK

rising edge. Therefore, the read transfer does not require any

synchronization logic (the

SBYPASS

signal is HIGH).

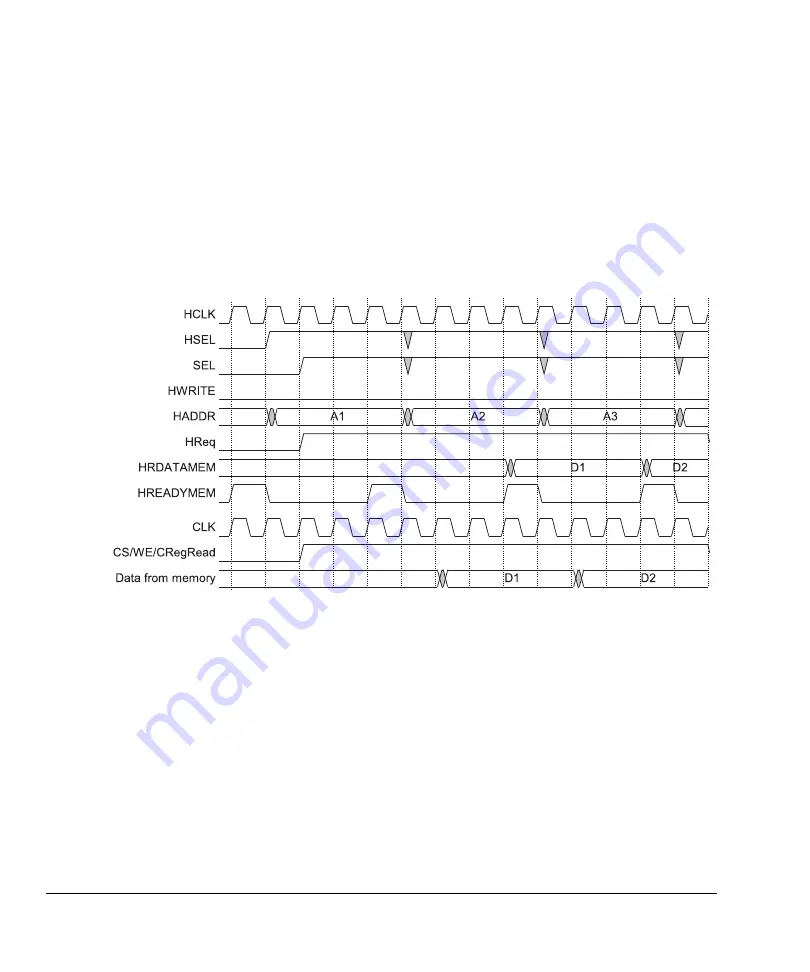

A software read cycle with

CLK

and

HCLK

synchronous is shown in Figure 2-9 on

page 2-21. The pipelined nature of the ETB11 data means that data takes more than a

single cycle to perform a read (and write) operation. Wait states are inserted until the

read cycle is completed.

Figure 2-10 Software read cycle with synchronous CLK and HCLK

2.11.2

Write transfer

Two types of write transfer are described:

•

•

Asynchronous HCLK and CLK

The relationship between

HReq

and

CReq

, and

CAck

and

HAck

is the same as it is for

a read transfer.

Summary of Contents for ETB11

Page 6: ...List of Tables vi Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 8: ...List of Figures viii Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 46: ...Functional Description 2 26 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 70: ...Signal Descriptions A 6 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 78: ...Glossary Glossary 4 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...