EM78P911A

8-bit Micro-controller

__________________________________________________________________________________________________________________________________________________________________

* This specification is subject to change without notice.

~ ~

12

12/19/2005 (V2.1)

LCD_C2,LCD_C1 LCD Display Control

LCD_M duty bias

0 0

change duty

Disable(turn off LCD)

0

1

1/16 1/4

1/8 1/4

0 1

Blanking

:

:

1 1

LCD display enable

:

:

* Bit3 (/WURING, RING Wake Up Enable): used to enable the wake-up function of /RINGTIME input pin.

(1/0=enable/disable)

* Bit4 (/WUP9L, PORT9 low nibble Wake Up Enable): used to enable the wake-up function of low nibble in

PORT9.(1/0=enable/disable)

* Bit5 (/WUP9H, PORT9 high nibble Wake Up Enable): used to enable the wake-up function of high nibble in

PORT9.(1/0=enable/disable)

* Bit6 (/WDTE,Watch Dog Timer Enable)

Control bit used to enable Watchdog timer.(1/0=enable/disable)

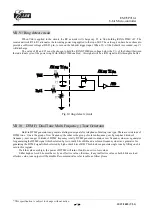

The relation between Bit3 to Bit6 can see the diagram 9.

* Bit7(Power control of Call Waiting circuit)

(1/0=enable circuit /disable circuit)

When Call waiting circuit is powered on, PLL is also enabled regardless of RA bit6(/358E). When Call

waiting circuit is powered off, PLL status is depended on RA bit6(/358E) setting.

/WURING

/RINGTIME

/WUP9L

PORT9(3:0)

/WUP9H

PORT9(7:4)

/WDTE

/WDTEN 0/1=enable/disable

Fig.9 Wake up function and control signal

12. RF (Interrupt Status Register)

7

6

5

4 3 2 1 0

INT3 FSK/CW

C8_2

C8_1

INT2 INT1 INT0

TCIF

* "1" means interrupt request, "0" means non-interrupt

* Bit 0 (TCIF) TCC timer overflow interrupt flag. Set when TCC timer overflows .

* Bit 1 (INT0) external INT0 pin interrupt flag .

* Bit 2 (INT1) external INT1 pin interrupt flag .

* Bit 3 (INT2) external INT2pin interrupt flag .

* Bit 4 (C8_1) internal 8 bit counter interrupt flag .

* Bit 5 (C8_2) internal 8 bit counter interrupt flag .

* Bit 6 ( FSK/CW ) FSK data or Call waiting data interrupt flag

* Bit 7 (INT3) external INT3 pin interrupt flag.

* High to low edge trigger , Refer to the Interrupt subsection.

* IOCF is the interrupt mask register. User can read and clear.

13. R10~R3F (General Purpose Register)

* R10~R3F (Banks 0~3) all are general purpose registers.

VII.2 Special Purpose Registers

1. A (Accumulator)

* Internal data transfer, or instruction operand holding

* It's not an addressable register.