Functional Architecture

Intel® Server Board SE7520AF2 TPS

50

Revision

1.2

Intel order number C77866-003

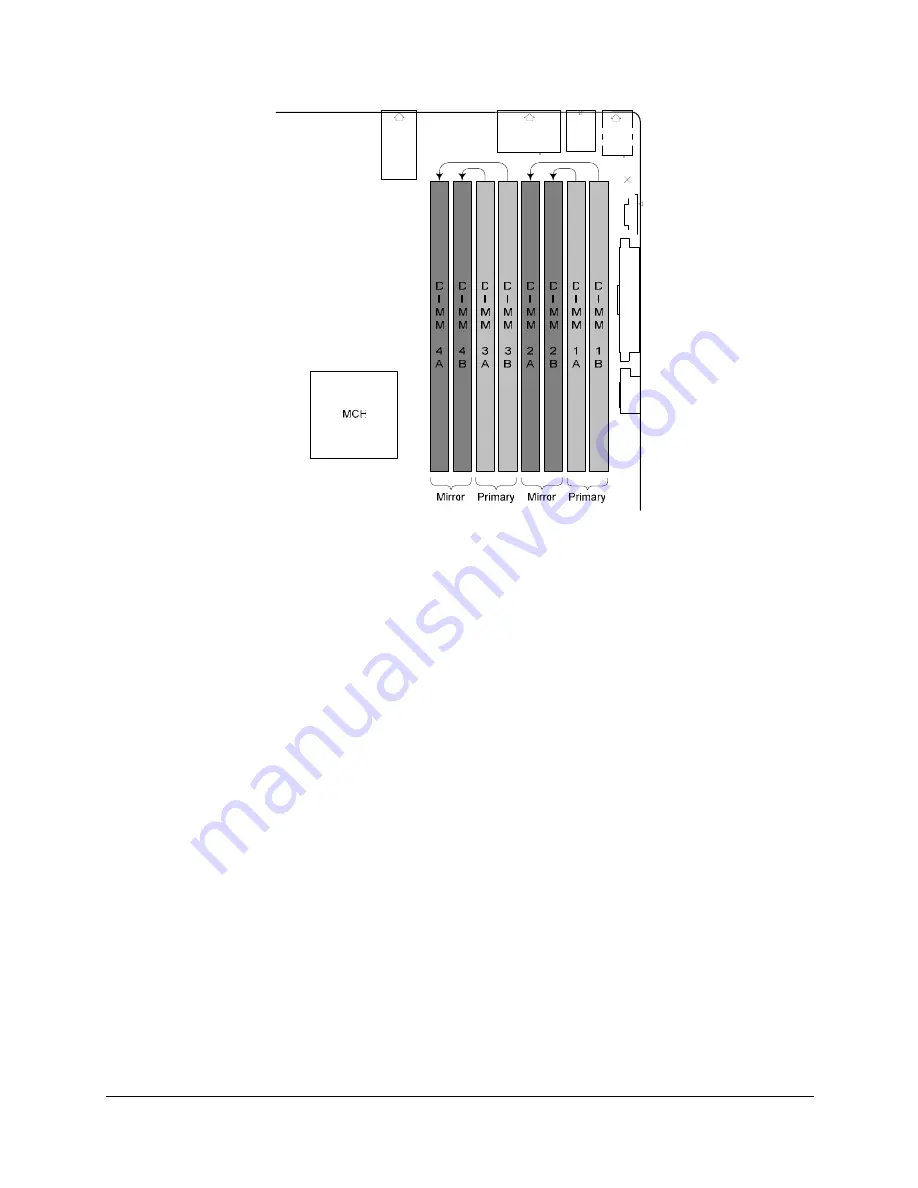

Figure 9. Eight DIMM Memory Mirror Configuration

The symmetry requirements are a result of the hardware mechanism for maintaining two copies

of all main memory data while ensuring that each channel has a full copy of all data in

preparation for fail-down to single-channel operation. Every write to memory is issued twice,

once to the “primary” location, and again to the “mirror” location. The data interleaved across the

channel pair are swapped for the second write (1A is a copy of 2B, 1B is a copy of 2A etc.). The

resulting memory image has two full copies of all data, and a complete copy is available on

each channel.

Hardware in the MCH tracks which DIMM slots are primaries, and which are mirrors, such that

data may be internally realigned to correctly reassemble cache lines regardless of which copy is

retrieved. There are four distinct cases for retrieval of the “even” and “odd” chunks of a cache-

line of data:

Interleaved dual-channel read to the primary DIMM with “even” data on channel A

Interleaved dual-channel read to the mirror DIMM with “even” data on channel B

Non-interleaved single-channel read pair to channel A with “even” data on the primary

DIMM

Non-interleaved single-channel read pair to channel B with “even” data on the mirror

DIMM

When mirroring is enabled via the MCH configuration, the memory subsystem maintains two

copies of all data, as described above, and retrieves requested data from either the primary

DIMM or the mirrored DIMM, based on the state of system address bit 15 (SA[15]).