MSM9225B User’s Manual

Chapter 2 Register Descriptions

2 – 37

2.4.13 Transmit Error Counter (TEC: AEhex)

TEC is a register to indicate the Transmit Error Counter value. This register is read-only.

At reset or when in the bus off state, TEC is set to “0000 0000”.

The bit configuration is shown below.

MSB

TEC7

TEC6

TEC5

TEC4

TEC3

TEC2

TEC1

TEC0

LSB

TEC (AEhex), R/W: R

Initial

value:

0

0

0

0

0

0

0

0

Figure 2-36 Transmit Error Counter (TEC)

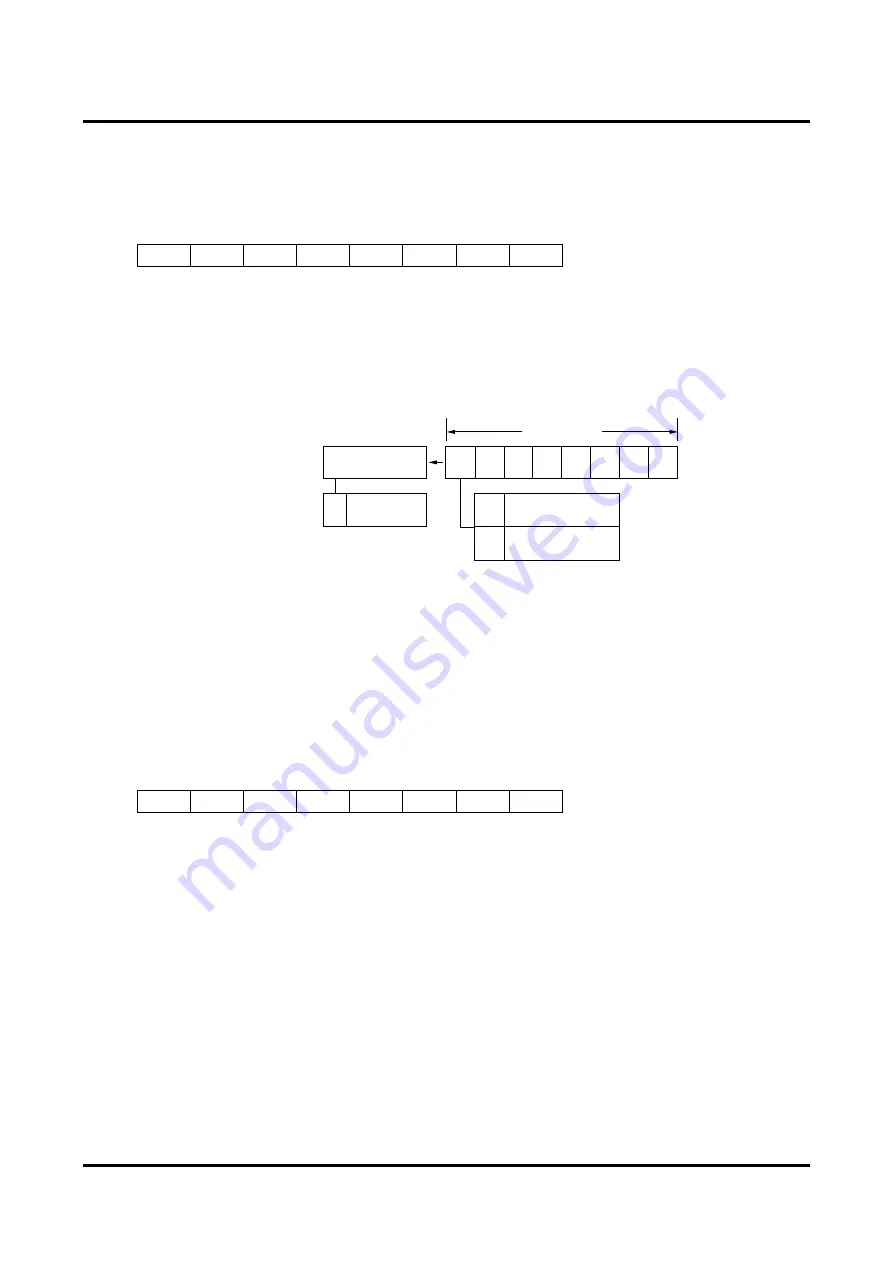

Figure 2-37 shows the relation between the Transmit Error Counter and the bus off flag (BOFF).

Bit 8 of the transmit error counter, which consists of 9 bits, indicates the BOFF value of the CAN status

register (CANS: 9Fhex); bit 7 indicates the TEP value of CANS.

7

1

BOFF

Bus off state

6

0

1

5

4

3

2

1

0

Transmit Error

Counter

TEC (AEhex)

Error active state

Error passive state

CANS (9Fhex): bit 6 = BOFF, bit 5 = TEP

Figure 2-37 Relation between the Transmit Error Counter and the Bus OFF flag

2.4.14 Receive Error Counter (REC: AFhex)

REC is a register to indicate the Receive Error Counter value. This register is read-only.

At reset or when in the bus off state, REC is set to “0000 0000”.

Bit 7 of the Receive Error Counter indicates the value of REP bit of the CAN status register (CANS: 9Fhex).

The bit configuration is shown below.

MSB

REC7

REC6

REC5

REC4

REC3

REC2

REC1

REC0

LSB

REC (AFhex), R/W: R

Initial

value:

0

0

0

0

0

0

0

0

Figure 2-38 Receive Error Counter (REC)

Summary of Contents for MSM9225B

Page 7: ...Chapter 1 Overview...

Page 13: ...Chapter 2 Register Descriptions...

Page 53: ...Chapter 3 Operational Description...

Page 62: ...Chapter 4 Microcontroller Interface...

Page 71: ...Chapter 5 Electrical Characteristics...

Page 81: ...Appendixes...