FPGA Registers

EPU-4562 Programmer’s Reference Manual

20

SPI

D

ATA

R

EGISTERS

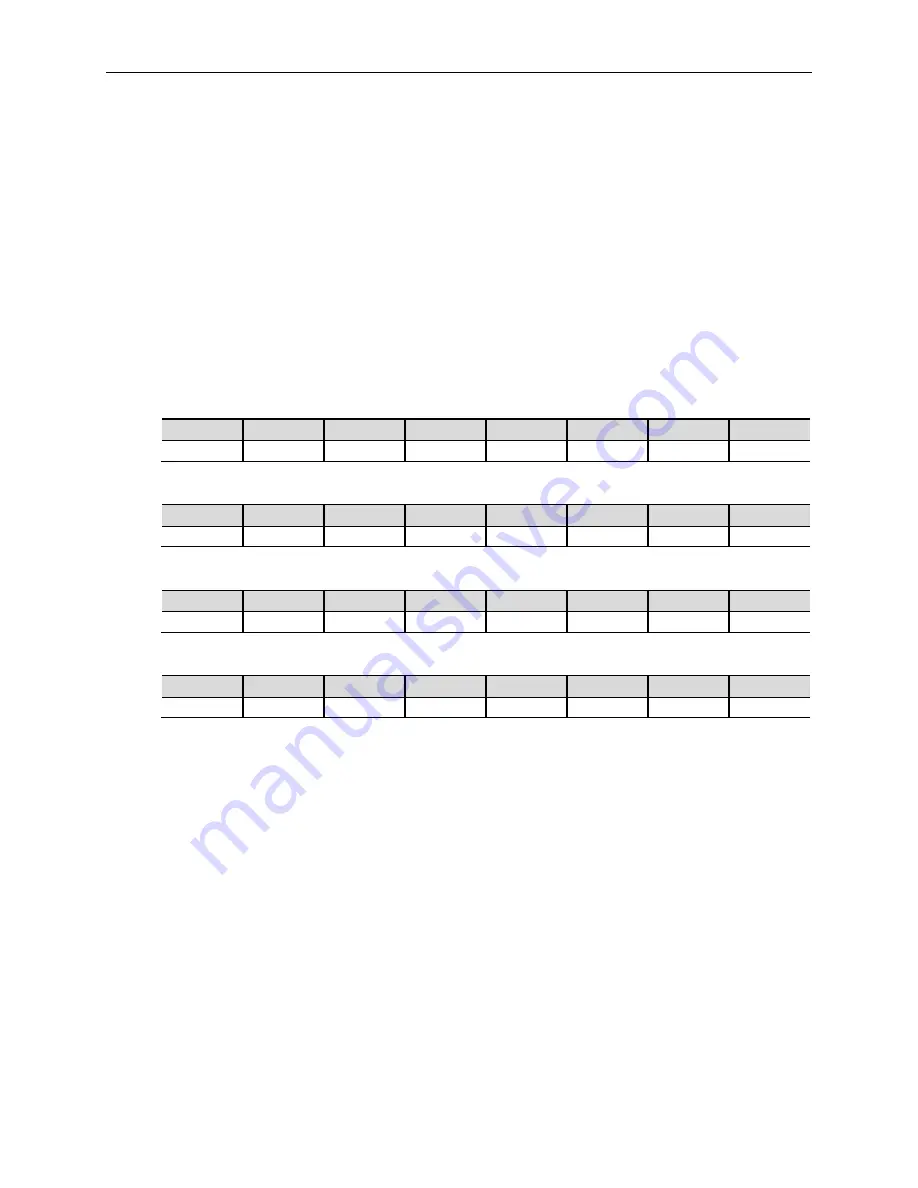

There are four data registers used on the SPI interface. How many are used depends on the

device being communicated with. SPIDATA0 is typically the least significant byte and

SPIDATA3 is the most significant byte. Any write to the most significant byte SPIDATA3

initiates the SCLK and, depending on the MAN_SS state, will assert a slave select to begin an

SPI bus transaction.

Data is sent according to the LSBIT_1ST setting. When LSBIT_1ST = 0, the MSbit of

SPIDATA3 is sent first and received data will be shifted in the LSbit of the selected frame size

determined by SPILEN1 and SPILEN0. When LSBIT_1ST = 1, the LSbit of the selected frame

size is sent first and the received data will be shifted in the MSbit of SPIDATA3.

SPIDATA0 (Least Significant Byte)

D7

D6

D5

D4

D3

D2

D1

D0

MSB

LSB

SPIDATA1

D7

D6

D5

D4

D3

D2

D1

D0

MSB

LSB

SPIDATA2

D7

D6

D5

D4

D3

D2

D1

D0

MSB

LSB

SPIDATA3 (Most Significant Byte) [Cycle Trigger Register]

D7

D6

D5

D4

D3

D2

D1

D0

MSB

LSB