AXI Bridge for PCI Express v2.4

21

PG055 June 4, 2014

Chapter 2:

Product Specification

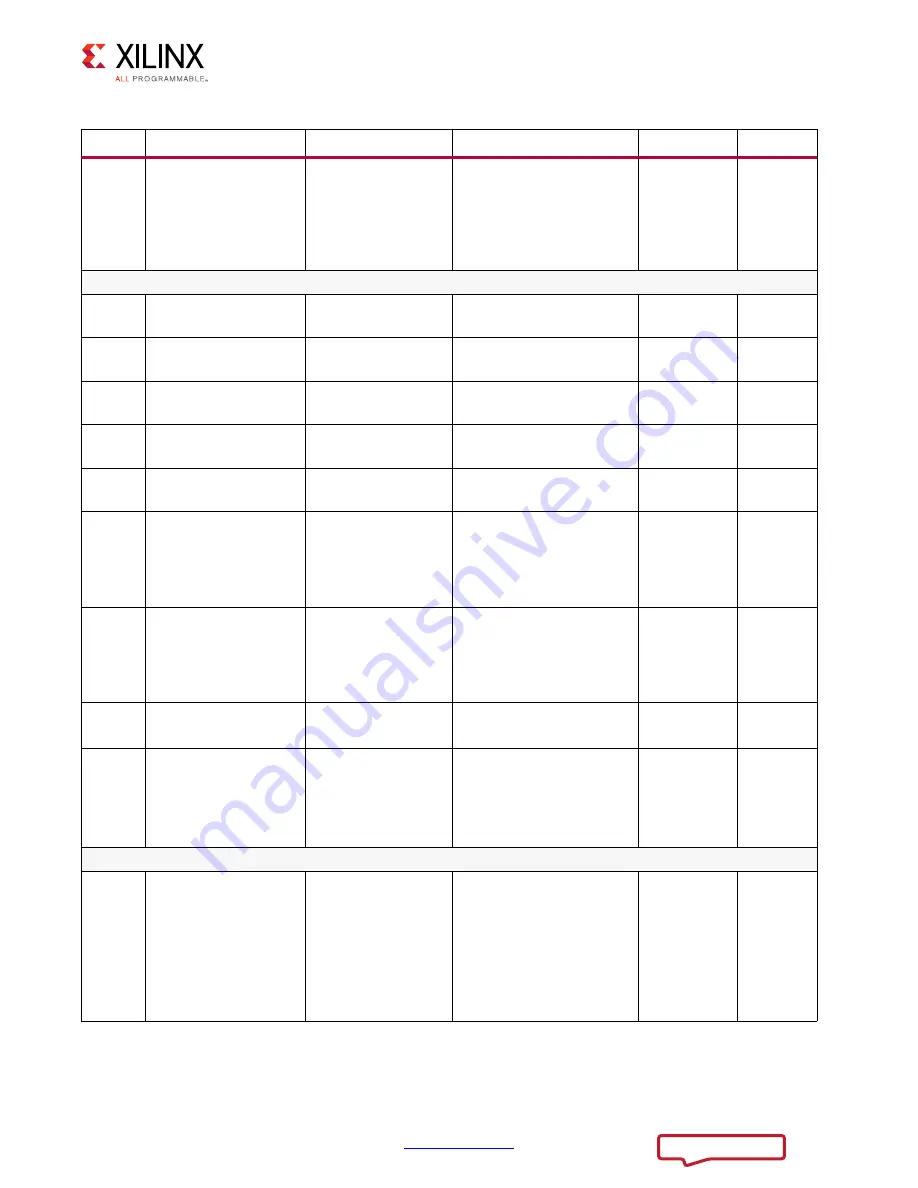

C_NUM_MSI_REQ

Specifies the size of

the MSI request

vector for selecting

the number of

requested message

values.

0-5

0

Integer

Memory Mapped AXI4 Parameters

G50

C_M_AXI_DATA_

WIDTH

AXI Master Bus Data

width

64: 7 series FPGAs only

128: 7 series FPGAs only

64

Integer

G51

C_M_AXI_ADDR_

WIDTH

AXI Master Bus

Address width

32

32

Integer

G52

C_S_AXI_ID_WIDTH

AXI Slave Bus ID

width

4

4

Integer

G53

C_S_AXI_DATA_

WIDTH

AXI Slave Bus Data

width

64: 7 series FPGAs only

128: 7 series FPGAs only

64

Integer

G54

C_S_AXI_ADDR_

WIDTH

AXI Slave Bus

Address width

32

32

Integer

C_M_AXI_PROTOCOL

Protocol definition

for M_AXI (Master

Bridge) port on AXI

Interconnect in the

Vivado IP integrator.

AXI4

AXI4

String

C_S_AXI_PROTOCOL

Protocol definition

for S_AXI (Slave

Bridge) port on AXI

Interconnect in the

Vivado IP integrator.

AXI4

AXI4

String

G55

C_MAX_LINK_

SPEED

Maximum PCIe link

speed supported

0: 2.5 GT/s - 7 series

1: 5.0 GT/s - 7 series

0

Integer

G56

C_INTERRUPT_PIN

Legacy INTX pin

support/select

0: No INTX support

(setting for Root Port)

1: INTA selected (only

allowable when core in

Endpoint configuration)

0

Integer

AXI4 Interconnect Parameters

G57

NUM_WRITE_

OUTSTANDING

AXI Interconnect

Slave Port Write

Pipeline Depth

1: Only one active AXI

AWADDR can be accepted

in the AXI slave bridge for

PCIe

2: Maximum of two active

AXI AWADDR values can

be stored in AXI slave

bridge for PCIe

2

Integer

Table 2-4:

Top-Level Parameters

(Cont’d)

Generic

Parameter Name

Description

Allowable Values

Default Value VHDL Type