AXI Bridge for PCI Express v2.4

31

PG055 June 4, 2014

Chapter 2:

Product Specification

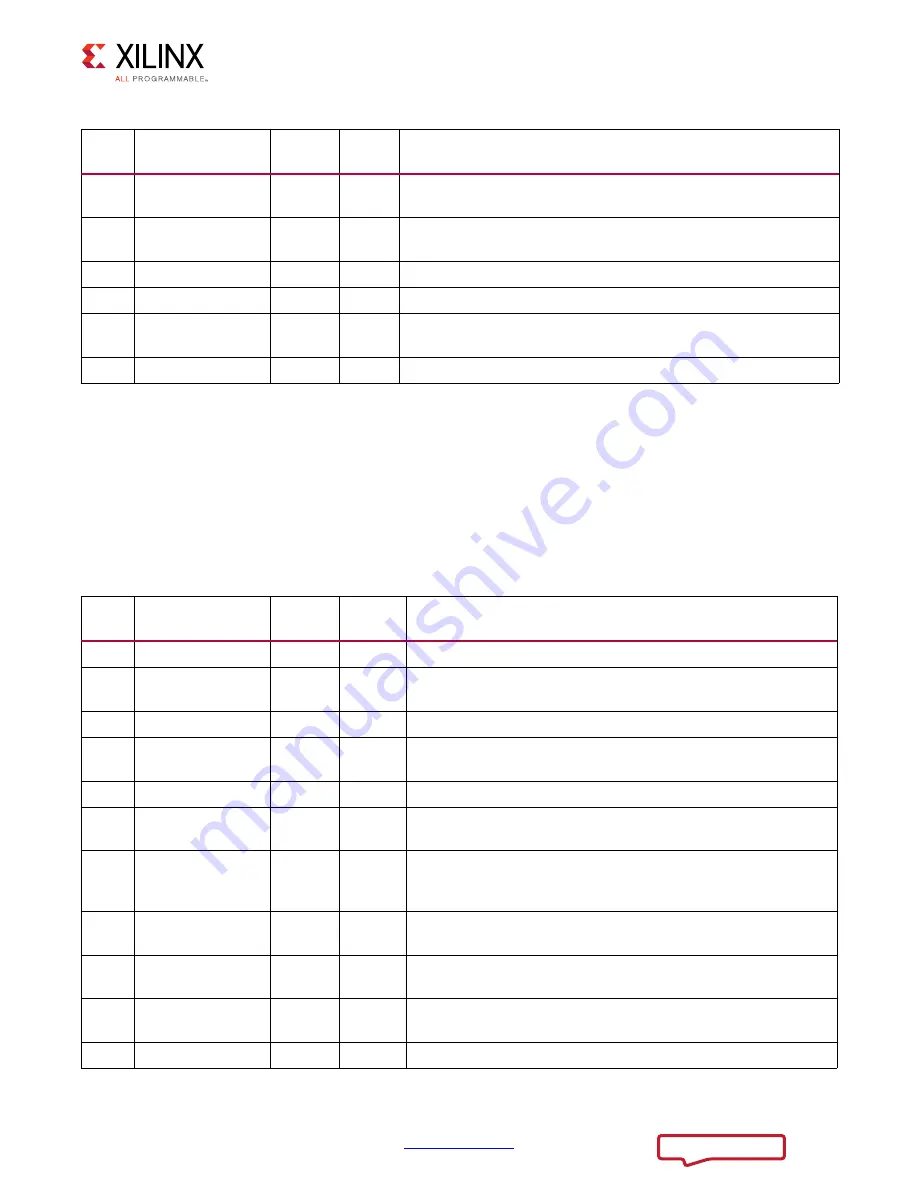

Interrupt Mask Register (Offset 0x13C)

The Interrupt Mask register controls whether each individual interrupt source can cause the

interrupt line to be asserted. A one in any location allows the interrupt source to assert the

interrupt line. The Interrupt Mask register initializes to all zeros. Therefore, by default no

interrupt is generated for any event.

describes the Interrupt Mask register bits

and values.

24

Slave Completer

Abort

RW1C

0

Indicates that a completion TLP was received with a status of

0b100 - Completer Abort.

25

Slave Illegal Burst RW1C

0

Indicates that a burst type other than INCR was requested by the

AXI master.

26

Master DECERR

RW1C

0

Indicates a Decoder Error (DECERR) response was received.

27

Master SLVERR

RW1C

0

Indicates a Slave Error (SLVERR) response was received.

28

Master Error

Poison

RW1C

0

Indicates an EP bit was set in a MemWR TLP for PCIe.

31:29 Reserved

RO

0

Reserved

Table 2-12:

Interrupt Decode Register

(Cont’d)

Bits

Name

Core

Access

Reset

Value

Description

Table 2-13:

Interrupt Mask Register

Bits

Name

Core

Access

Reset

Value

Description

0

Link Down

RW

0

Enables interrupts for Link Down events when bit is set.

1

ECRC Error

RW

0

Enables interrupts for ECRC Error events when bit is set.

(Only writable for EP configurations, otherwise = ‘0’)

2

Streaming Error

RW

0

Enables interrupts for Streaming Error events when bit is set.

3

Hot Reset

RW

0

Enables interrupts for Hot Reset events when bit is set.

(Only writable for EP configurations, otherwise = ‘0’)

4

Reserved

RO

0

Reserved

7:5

Cfg Completion

Status

RW

0

Enables interrupts for config completion status.

(Only writable for Root Port Configurations, otherwise = ‘0’)

8

Cfg Timeout

RO

0

Enables interrupts for Config (Cfg) Timeout events when bit is

set.

(Only writable for Root Port Configurations, otherwise = ‘0’)

9

Correctable

RO

0

Enables interrupts for Correctable Error events when bit is set.

(Only writable for Root Port Configurations, otherwise = ‘0’)

10

Non-Fatal

RO

0

Enables interrupts for Non-Fatal Error events when bit is set.

(Only writable for Root Port Configurations, otherwise = ‘0’)

11

Fatal

RO

0

Enables interrupts for Fatal Error events when bit is set.

(Only writable for Root Port Configurations, otherwise = ‘0’)

15:12 Reserved

RO

0

Reserved