Transmit Flow Control Interface

The following table defines the transmit flow control interface ports of the core.

Note: The

pcie0*

signals map to PCIe Controller 0 and

pcie1*

signals map to PCIe Controller 1 in the

port descriptions below.

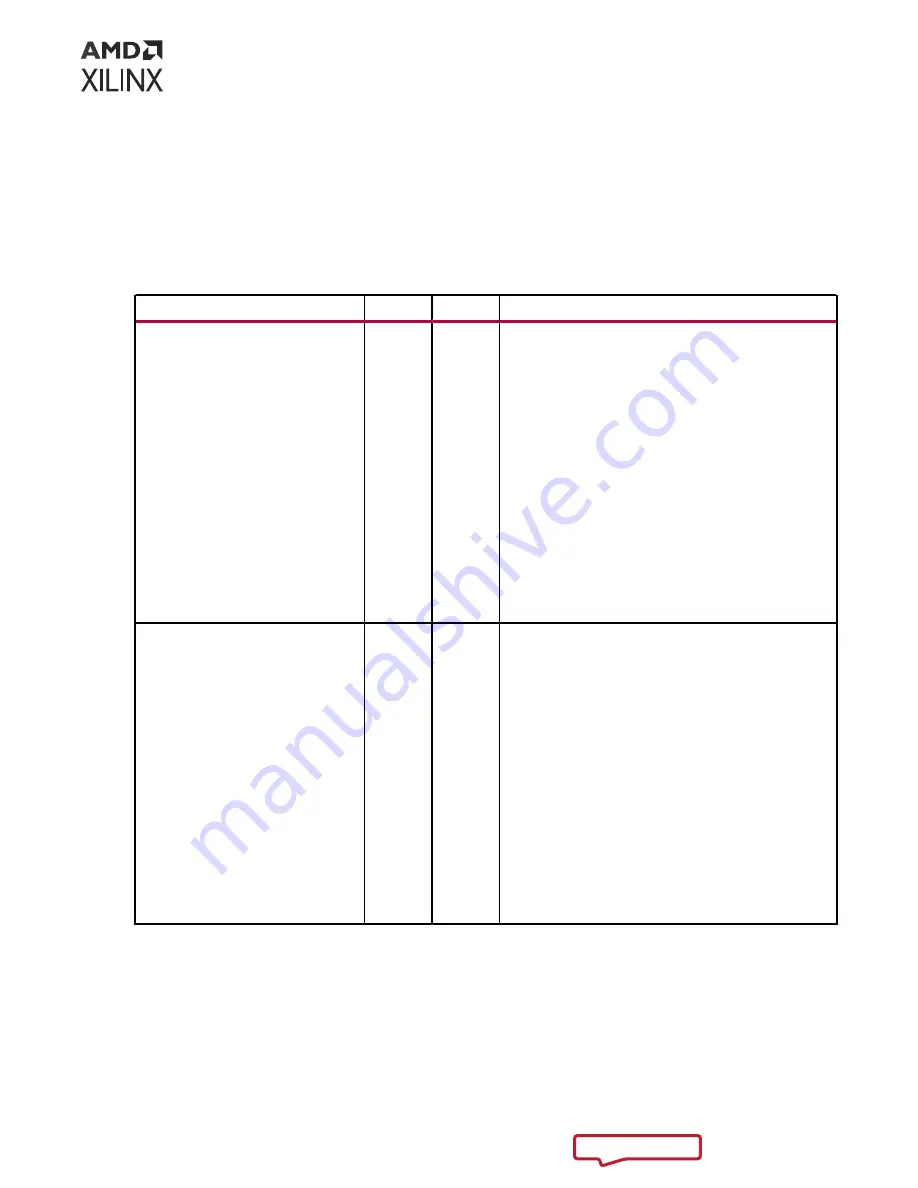

Table 38: Transmit Flow Control Interface Port Description

Port

I/O

Width

Description

pcie0_pcie_tfc_nph_av

pcie1_pcie_tfc_nph_av

O

4

This output provides an indication of the currently

available header credit for Non-Posted TLPs on the

transmit side of the core. The user logic can check this

output before transmitting a Non-Posted request on the

requester request interface to avoid blocking the

interface when no credit is available. The encodings are:

•

0000: No credit available

•

0001: 1 credit available

•

0010: 2 credits available

•

...

•

1110: 14 credits available

•

1111: 15 or more credits available

Because of pipeline delays, the value on this output can

not include the credit consumed by the Non-Posted

requests in the last eight cycles or less. The user logic

must adjust the value on this output by the credit

consumed by the Non-Posted requests it sent in the

previous clock cycles, if any.

pcie0_pcie_tfc_npd_av

pcie1_pcie_tfc_npd_av

O

4

This output provides an indication of the currently

available payload credit for Non-Posted TLPs on the

transmit side of the core. The user logic checks this

output before transmitting a Non-Posted request on the

requester request interface to avoid blocking the

interface when no credit is available. The encodings are:

•

0000: No credit available

•

0001: 1 credit available

•

0010: 2 credits available

•

...

•

1110: 14 or more credits available

•

1111: 15 or more credits available

Because of pipeline delays, the value on this output does

not include the credit consumed by the Non-Posted

requests sent by the user logic in the last eight clock

cycles or less. The user logic must adjust the value on this

output by the credit consumed by the Non-Posted

requests it sent in the previous clock cycles, if any.

Configuration Control Interface

The Configuration Control interface signals allow a broad range of information exchange

between the user application and the core. The user application uses this interface to do the

following:

Chapter 3: Product Specification

PG346 (v3.3) November 16, 2022

CPM Mode for PCI Express

108