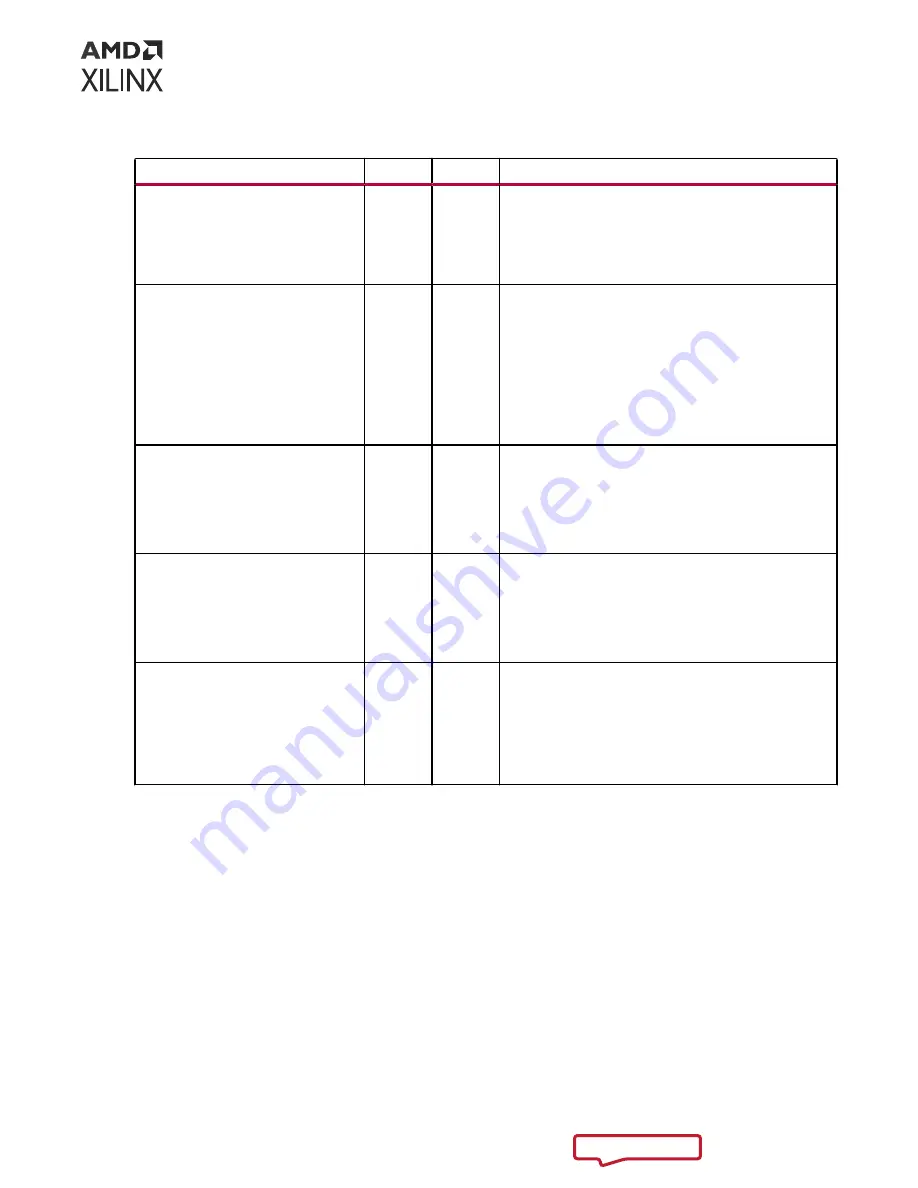

Table 43: MSI-X Interrupt Internal Interface Port Descriptions (cont'd)

Name

I/O

Width

Description

pcie0_cfg_msix_vec_pending_status

O

1

Configuration Interrupt MSI-X Pending Bit Status

This output provides the status of the Pending Bit

associated with an MSI-X interrupt, in response to query

using the pcie(n)_cfg_msix_vec_pending input.

It is active only when the core is configured to include the

MSI-X Table and Pending Bit Array.

pcie0_cfg_msi_attr

pcie1_cfg_msi_attr

I

3

Configuration Interrupt MSI/MSI-X TLP Attribute

These bits enable you to set the Attribute bits that are

used for both MSI and MSI-X interrupt requests.

•

Bit 0 is the No Snoop bit.

•

Bit 1 is the Relaxed Ordering bit.

•

Bit 2 is the ID-Based Ordering bit.

The core samples these bits on a 0-to-1 transition on

pcie(n)_cfg_msi_mint_vector bits (when using MSI) or

pcie(n)_cfg_msix_int_vector (when using MSI-X).

pcie0_cfg_msi_tph_present

pcie1_cfg_msi_tph_present

I

1

Configuration Interrupt MSI/MSI-X TPH Present

Indicates the presence of an optional Transaction

Processing Hint (TPH) in the MSI/MSI-X interrupt request.

The user application must set this bit while asserting

pcie(n)_cfg_msi_mint_vector bits (when using MSI), or

pcie(n)_cfg_msix_int_vector (when using MSI-X), if it is

including a TPH in the MSI or MSI-X transaction.

pcie0_cfg_msi_tph_type

pcie1_cfg_msi_tph_type

I

2

Configuration Interrupt MSI/MSI-X TPH Type

When pcie(n)_cfg_msi_tph_present is 1'b1, these two bits

are used to supply the 2-bit type associated with the Hint.

The core samples these bits on 0-to-1 transition on any bit

of pcie(n)_cfg_msi_mint_vector or

pcie(n)_cfg_msix_int_vector, depending on whether MSI

or MSI-X interrupts are being used.

pcie0_cfg_msi_tph_st_tag

pcie1_cfg_msi_tph_st_tag

I

8

Configuration Interrupt MSI/MSI-X TPH Steering Tag

When pcie(n)_cfg_msi_tph_present is asserted, the

SteeringTag associated with the Hint must be placed on

pcie(n)_cfg_msi_tph_st_tag[7:0]. The core samples these

bits on 0-to-1 transition on any bit of

pcie(n)_cfg_msi_mint_vector or

pcie(n)_cfg_msix_int_vector, depending on whether MSI

or MSI-X interrupts are being used.

Configuration Extend Interface

The Configuration Extend interface allows the core to transfer configuration information with the

user application when externally implemented configuration registers are implemented. The

following table defines the ports in the Configuration Extend interface of the core.

Note: The

pcie0*

signals map to PCIe Controller 0 and

pcie1*

signals map to PCIe Controller 1 in the

port descriptions below.

Chapter 3: Product Specification

PG346 (v3.3) November 16, 2022

CPM Mode for PCI Express

119