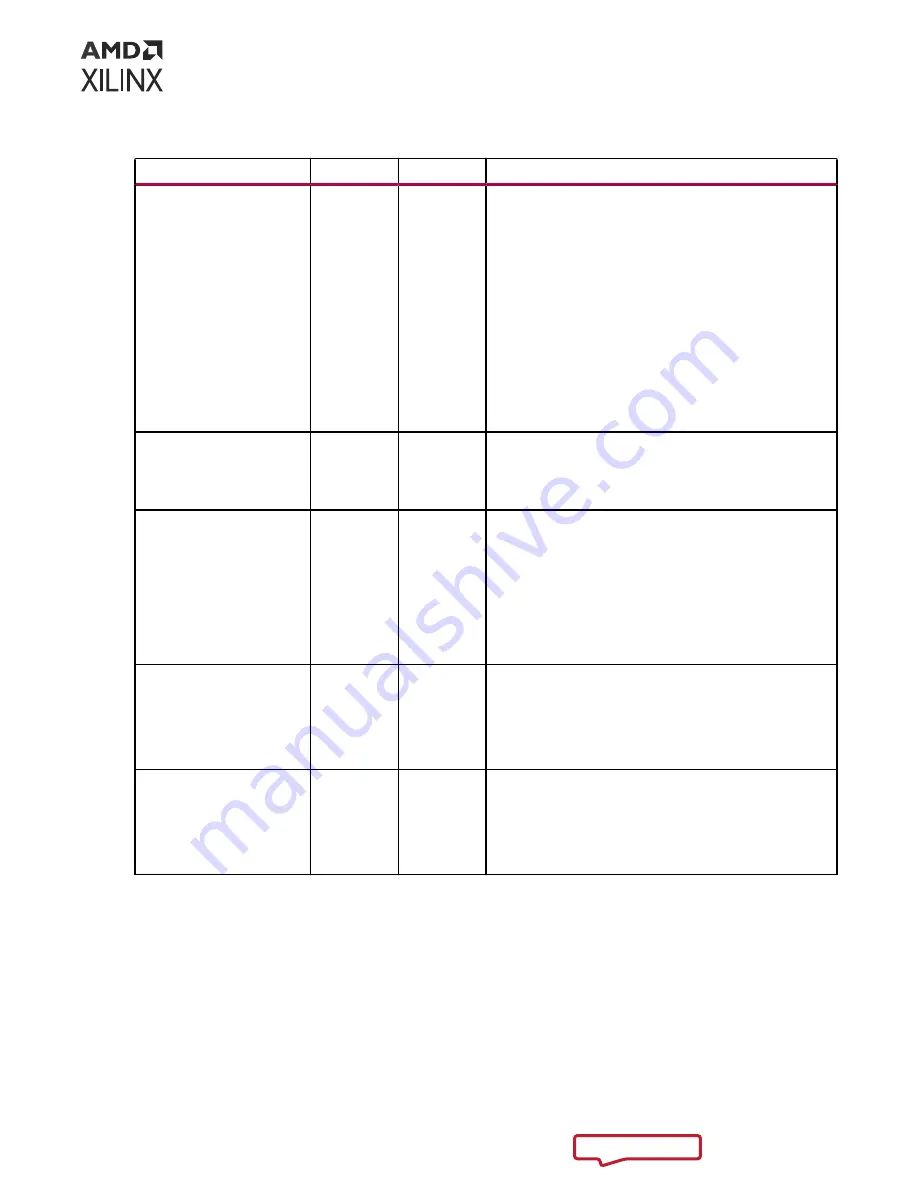

Table 26: Requester Request Interface Port Descriptions (1024-bit Interface) (cont'd)

Name

Width

I/O

Description

pcie0_s_axis_rq_tkeep

pcie1_s_axis_rq_tkeep

32

I

The assertion of bit i of this bus during a transfer indicates

to the core that Dword i of the pcie(n)_s_axis_rq_tdata bus

contains valid data. The user logic must set this bit to 1

contiguously for all Dwords starting from the first Dword of

the descriptor to the last Dword of the payload. Thus,

pcie(n)_s_axis_rq_tdata must be set to all 1s in all beats of a

packet, except in the final beat when the total size of the

packet is not a multiple of the width of the data bus (both in

Dwords). This is true for both Dword-aligned and 128b

address-aligned modes of payload transfer.

The tkeep bits are valid only when straddle is not enabled

on the RQ interface. When straddle is enabled, the core

ignores the setting of these bits when receiving data across

the interface. The user logic must set the is_sop/is_eop

signals in the pcie(n)_s_axis_rq_tuser bus in that case to

signal the start and end of TLPs transferred over the

interface.

pcie0_s_axis_rq_tvalid

pcie1_s_axis_rq_tvalid

1

I

The user application must assert this output whenever it is

driving valid data on the pcie(n)_s_axis_rq_tdata bus. The

user application must keep the valid signal asserted during

the transfer of a packet. The core paces the data transfer

using the pcie(n)_s_axis_rq_tready signal.

pcie0_s_axis_rq_tready

pcie1_s_axis_rq_tready

1

O

Activation of this signal by the PCIe core indicates that it is

ready to accept data. Data is transferred across the interface

when both pcie(n)_s_axis_rq_tvalid and

pcie(n)_s_axis_rq_tready are asserted in the same cycle.

If the core deasserts the ready signal when the valid signal

is High, the user logic must maintain the data on the bus

and keep the valid signal asserted until the core has

asserted the ready signal.

With this output port, each bit indicates the same value, so

the user logic can use any of the bit.

pcie0_rq_tag_vld0

pcie1_rq_tag_vld0

1

O

The core asserts this output for one cycle when it has

allocated a tag to an incoming Non-Posted request from the

requester request interface and placed it on the

pcie(n)_rq_tag0 output. The bit is encoded as follows:

•

0: No tags being provided in this cycle.

•

1: A tag is presented on pcie(n)_rq_tag0.

pcie0_rq_tag_vld1

pcie1_rq_tag_vld1

1

O

The core asserts this output for one cycle when it has

allocated a tag to an incoming Non-Posted request from the

requester request interface and placed it on the

pcie(n)_rq_tag1 output. The bit is encoded as follows:

•

0: No tag is provided on pcie(n)_rq_tag1 in this cycle.

•

1: A tag is presented on pcie(n)_rq_tag1.

Chapter 3: Product Specification

PG346 (v3.3) November 16, 2022

CPM Mode for PCI Express

81