Bus Interface Unit

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

6-9

cannot detect a sequential access and use an address incrementer to perform

back-to-back sequential cycles. All instruction fetches are treated as non-sequential

accesses.

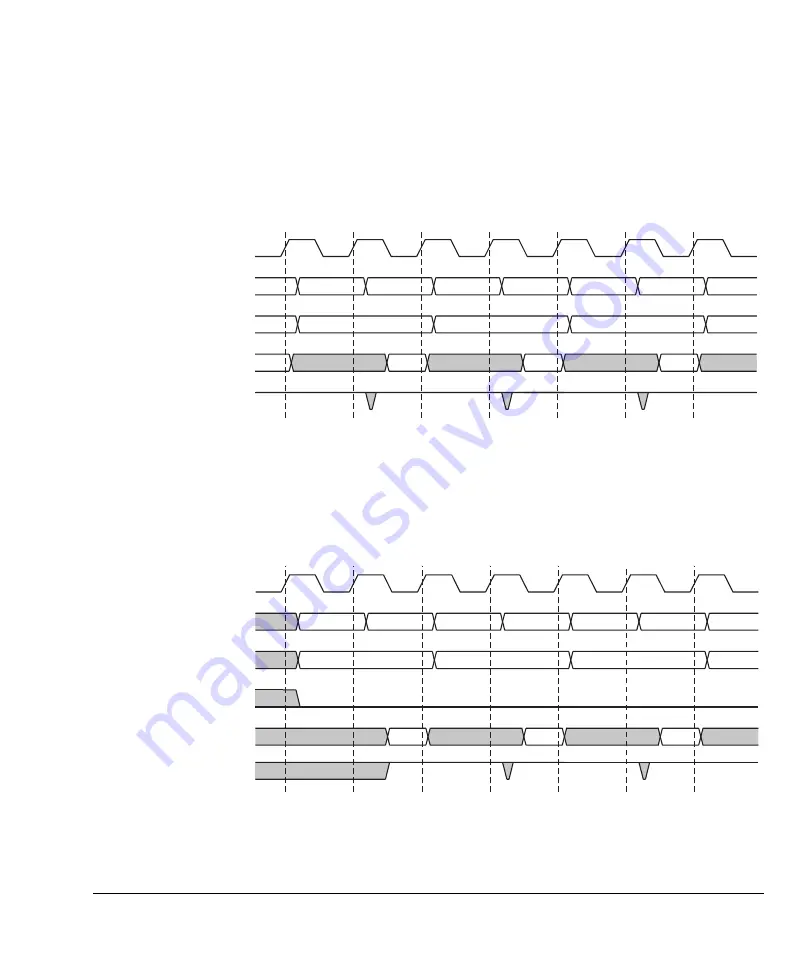

Figure 6-3 shows a series of sequential instruction fetches where any data access being

performed by the ARM9E-S is using the tightly-coupled SRAM. Therefore, data

accesses do not interfere with the instruction fetches.

Figure 6-3 Sequential instruction fetches, no AHB data access required

Back-to-back LDR or STR accesses

Figure 6-4 shows ARM966E-S bus activity when a sequence of LDR instructions is

executed.

Figure 6-4 Back-to-back LDR, no external instruction access

A series of NONSEQ/IDLE transfers is indicated for each access.

HTRANS

IDLE

NONSEQ

IDLE

NONSEQ

HADDR

HREADY

HRDATA

CLK

IDLE

NONSEQ

IDLE

NONSEQ

ID-3

ID-4

ID-2

ID-1

IA-4

IA-5

IA-3

IDLE

IA-2

HTRANS

NONSEQ

IDLE

NONSEQ

IDLE

NONSEQ

HADDR

DA-2

HWRITE

HREADY

HRDATA

DD-1

DD-3

CLK

DD-2

DA-1

DA-3

DA-4

NONSEQ

IDLE

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...