80

M3i.48xx / M3i.48xx-exp Manual

Overview

Clock generation

Clock generation

Overview

The different clock modes

The Spectrum M3i/M4i cards offer a wide variety of different clock modes

to match all the customers needs. All of the clock modes are described in de-

tail with programming examples in this chapter.

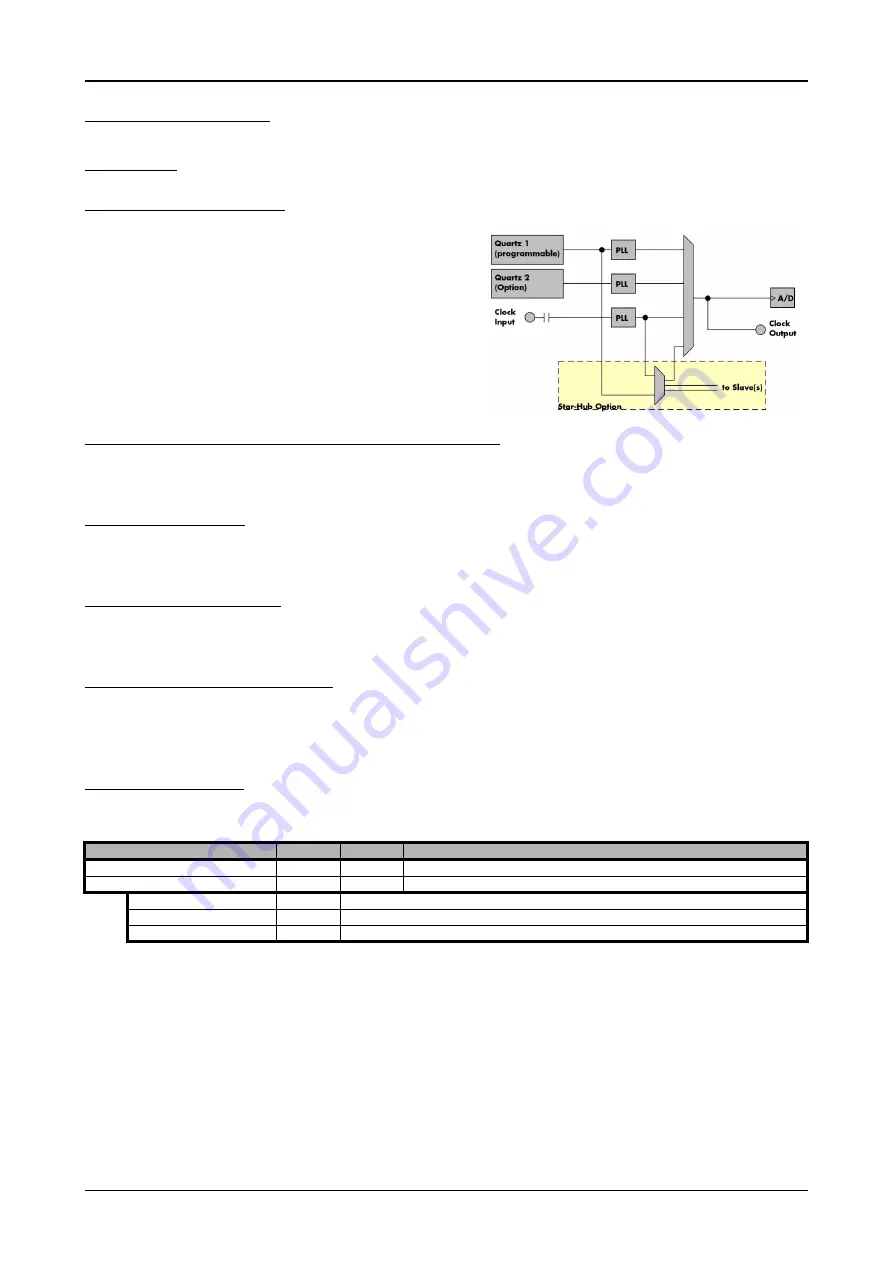

The figure is showing an overview of the complete engine used on all M3i/

M4i cards for clock generation.

The purpose of this chapter is to give you a guide to the best matching clock

settings for your specific application and needs.

Standard internal sample rate (programmable reference quartz 1)

This is the easiest and most common way to generate a sample rate with no need for additional external clock signals. The sample rate has

a very fine resolution, low jitter and a high accuracy. The Quartz 1 is a high quality software programmable clock device acting as a refer-

ence to the internal PLL. The specification is found in the technical data section of this manual.

Quartz2 with PLL (option)

This optional second Quartz 2 is for special customer needs, either for a special direct sampling clock or as a very precise reference for the

PLL. Please feel free to contact Spectrum for your special needs. The Quarz 2 clock footprint can be equipped with a wide variety of clock

sources that are available on the market.

External Clock (reference clock)

Any clock can be fed in that matches the specification of the board. The external clock signal can be used to synchronize the board on a

system clock or to feed in an exact matching sample rate. The external clock is divided/multiplied using a PLL allowing a wide range of

external clock modes.

Synchronization clock (option Star-Hub)

The star-hub option allows the synchronization of up to 8 cards of the M3i/M4i series from Spectrum with a minimal phase delay between

the different cards. The clock is distributed from the master card to all connected cards. As a source it is possible to either use the program-

mable Quarz 1 clock or the external clock input of the master card. For details on the synchronization option please take a look at the ded-

icated chapter later in this manual.

Clock Mode Register

The selection of the different clock modes has to be done by the SPC_CLOCKMODE register. All available modes, can be read out by the

help of the SPC_AVAILCLOCKMODES register.

The different clock modes and all other related or required register settings are described on the following pages.

Register

Value

Direction

Description

SPC_AVAILCLOCKMODES

20201

read

Bitmask, in which all bits of the below mentioned clock modes are set, if available.

SPC_CLOCKMODE

20200

read/write

Defines the used clock mode or reads out the actual selected one.

SPC_CM_INTPLL

1

Enables internal programmable high precision Quartz 1 for sample clock generation

SPC_CM_QUARTZ2

4

Enables optional Quartz 2 as reference for sample clock generation

SPC_CM_EXTREFCLOCK

32

Enables internal PLL with external reference for sample clock generation