Mode Multiple Recording

Trigger Modes

(c) Spectrum GmbH

105

Limits of pre trigger, post trigger, memory size

The maximum memory size parameter is only limited by the number of activated channels and by the amount of installed memory. Please

keep in mind that each samples needs 2 bytes of memory to be stored. Minimum memory size as well as minimum and maximum post trigger

limits are independent of the activated channels or the installed memory.

Due to the internal organization of the card memory there is a certain stepsize when setting these values that has to be taken into account.

The following table gives you an overview of all limits concerning pre trigger, post trigger, memory size, segment size and loops. The table

shows all values in relation to the installed memory size in samples. If more memory is installed the maximum memory size figures will increase

according to the complete installed memory

All figures listed here are given in samples. An entry of [32G - 8] means [32 GSamples - 8 ] = 34,359,738,360 samples.

The given memory and memory / divider figures depend on the installed on-board memory as listed below:

Please keep in mind that this table shows all values at once. Only the absolute maximum and minimum values are shown. There might be

additional limitations. Which of these values is programmed depends on the used mode. Please read the detailed documentation of the mode.

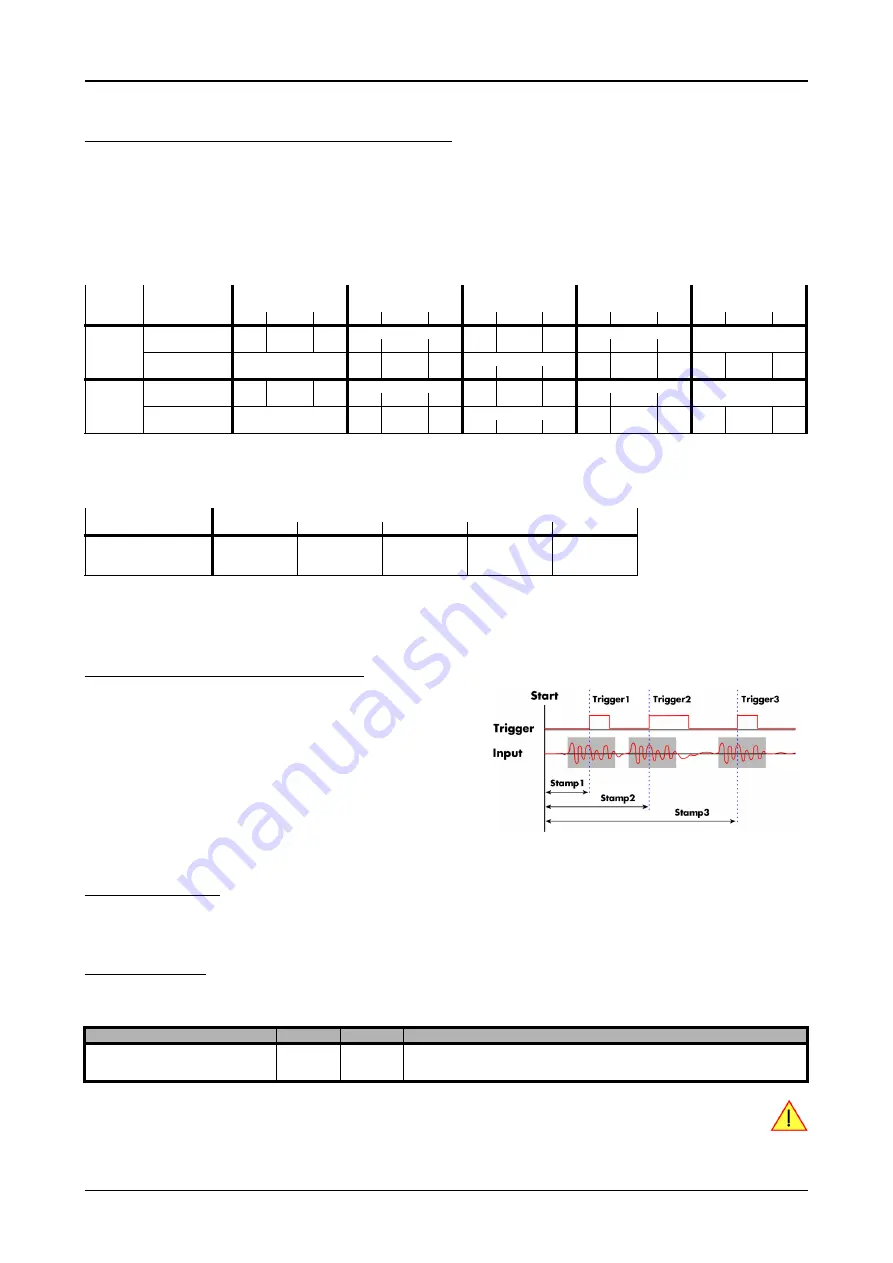

Multiple Recording and Timestamps

Multiple Recording is well matching with the timestamp option. If timestamp

recording is activated each trigger event and therefore each Multiple Re-

cording segment will get timestamped as shown in the drawing on the right.

Please keep in mind that the trigger events are timestamped, not the begin-

ning of the acquisition. The first sample that is available is at the time position

of [Timestamp - Pretrigger].

The programming details of the timestamp option is explained in an extra

chapter.

Trigger Modes

When using Multiple Recording all of the card’s trigger modes can be used except the software trigger. For detailed information on the avail-

able trigger modes, please take a look at the relating chapter earlier in this manual.

Trigger Counter

The number of acquired trigger events in Multiple Recording mode is counted in hardware and can be read out while the acquisition is running

or after the acquisition has finished. The trigger events are counted both in standard mode as well as in FIFO mode.

The trigger counter feature needs at least driver version V2.17 and firmware version V20 (M2i series), V10

(M3i series) or V6 (M4i series). Please update the driver and the card firmware to these versions to use this

feature. Trying to use this feature without the proper firmware version will issue a driver error.

Activated

Used

Memory size

Pre trigger

Post trigger

Segment size

Loops

Channels

Mode

SPC_MEMSIZE

SPC_PRETRIGGER

SPC_POSTTRIGGER

SPC_SEGMENTSIZE

SPC_LOOPS

Min

Max

Step

Min

Max

Step

Min

Max

Step

Min

Max

Step

Min

Max

Step

1 channel

Standard Single

16

Mem

8

defined by post trigger

8

8G - 8

8

not used

not used

Standard Multi/ABA 16

Mem

8

8

8k

8

8

Mem/2

8

16

Mem/2

8

not used

FIFO Single

not used

8

8k

8

not used

16

8G - 8

8

0 (

∞

)

4G - 1

1

FIFO Multi/ABA

not used

8

8k

8

8

8G - 8

8

16

pre+post

8

0 (

∞

)

4G - 1

1

2 channels

Standard Single

16

Mem/2

8

defined by post trigger

8

8G - 8

8

not used

not used

Standard Multi/ABA 16

Mem/2

8

8

4k

8

8

Mem/4

8

16

Mem/4

8

not used

FIFO Single

not used

8

4k

8

not used

16

8G - 8

8

0 (

∞

)

4G - 1

1

FIFO Multi/ABA

not used

8

4k

8

8

8G - 8

8

16

pre+post

8

0 (

∞

)

4G - 1

1

Installed Memory

128 MSample

256 MSample

512 MSample

1 GSample

2 GSample

Mem

128 MSample

256 MSample

512 MSample

1 GSample

2 GSample

Mem / 2

64 MSample

128 MSample

256 MSample

512 MSample

1 GSample

Mem / 4

32 MSample

64 MSample

128 MSample

256 MSample

512 MSample

Register

Value

Direction

Description

SPC_TRIGGERCOUNTER

200905

read

Returns the number of trigger events that has been acquired since the acquisiition start. The internal

trigger counter has 48 bits. It is therefore necessary to read out the trigger counter value with 64 bit

access or 2 x 32 bit access if the number of trigger events exceed the 32 bit range.