TOBY-L4 series - System Integration Manual

UBX-16024839 - R04

System description

Page 46 of 143

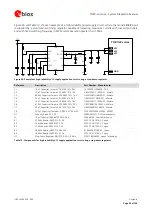

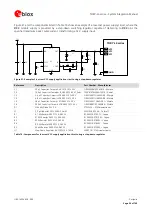

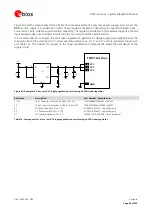

1.9.6

RGMII interface

RGMII interface is not supported by the "50" product version.

TOBY-L4 series modules include an Ethernet Media Access Control (MAC) block supporting up to 1 Gbit/s data

rate via a Reduced Gigabit Media-Independent Interface compliant with the

RGMII Version 1.3 specification

and the

RMII Revision 1.2 specification

The module represents an Ethernet MAC controller, which can be connected to an external Ethernet physical

transceiver (PHY) chip for communication with a remote processor over Ethernet.

The following signals are provided for communication and management of an external Ethernet PHY:

V_ETH

Interface supply output

ETH_TX_CLK

RGMII Transmit reference Clock (TXC) output

RMII Reference Clock (REF_CLK) output

ETH_TX_CTL

RGMII Transmit Control output, driven on both edges of the Transmit clock (TXC)

RMII Transmit Enable (TXEN) output, synchronous with Reference Clock (REF_CLK)

ETH_TXD0

RGMII / RMII Transmit Data [0], from MAC to PHY (module output)

ETH_TXD1

RGMII / RMII Transmit Data [1], from MAC to PHY (module output)

ETH_TXD2

RGMII Transmit Data [2], from MAC to PHY (module output)

ETH_TXD3

RGMII Transmit Data [3], from MAC to PHY (module output)

ETH_RX_CLK

RGMII Receive reference Clock (RXC) input

ETH_RX_CTL

RGMII Receive Control input, sampled on both edges of the Receive clock (RXC)

RMII Carrier Sense (CRS) / Receive Data Valid (RX_DV) input

ETH_RXD0

RGMII / RMII Receive Data [0], from PHY to MAC (module input)

ETH_RXD1

RGMII / RMII Receive Data [1], from PHY to MAC (module input)

ETH_RXD2

RGMII Receive Data [2], from PHY to MAC (module input)

ETH_RXD3

RGMII Receive Data [3], from PHY to MAC (module input)

ETH_INTR

Ethernet Interrupt Input, from PHY to MAC (module input)

When this signal is high, it indicates an interrupt event in the PHY

ETH_MDIO

Management Data Input Output, bidirectional signal (module input/output)

ETH_MDC

Management Data Clock, from MAC to PHY (module output)