30

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

System Monitor Control Logic

Supply Sensor Alarms

When the measured value on the supply sensor for V

CCINT

or V

CCAUX

is greater than the

thresholds in Control registers

51h

and

52h

, or less than the thresholds in Control registers

55h

and

56h

, then the output alarms go active. The alarms are reset when a subsequently

measured value falls inside the threshold.

Thermal Management

The on-chip temperature measurement is used for critical temperature warnings. The

default Over Temperature threshold is 125°C. This threshold is used for preconfiguration

or when the contents of the OT Upper alarm register have not been configured. To override

this default condition, the 10 MSBs of the OT Upper register (Control Register

53h

) must

be set using the temperature sensor transfer function (

). In addition, the four LSBs

must be set to

0011b

.

When the die temperature exceeds a factory set limit of 125°C or a user selected threshold,

the Over-Temperature alarm logic output (OT) becomes active. This feature can be

disabled by the user when System Monitor is instantiated in a design. The OT function is

disabled by writing a logic 1 to the OT bit in Configuration register 1. The OT signal resets

when the FPGA temperature has fallen below a user-programmable limit in Control

register

57h

(see

). When the automatic power-down feature is enabled,

the OT signal can be used to trigger a device power down. When OT goes active High, the

FPGA enters power down approximately 10 ms later. The power-down feature initiates a

configuration shutdown sequence disabling the device when finished and asserts GHIGH

to prevent any contention (see

Virtex-6 FPGA Configuration Guide

). When OT is deasserted,

GHIGH will also deassert and the startup sequence is initiated releasing all global

resources. By default this functionality is disabled and must be explicitly enabled. The

automatic power down is enabled by using a configuration option in the ISE™ software,

version 9.1i or later. Check the “Power Down Device if Over Safe Temperature” option

under “Configuration Options” on the Process Properties GUI for generating a

programming file. Alternatively use the

bitgen -g

command line option

OverTempPowerDown:[Enable¦Disable]

. When the FPGA enters power down,

System Monitor continues to operate in whatever mode was configured prior to power

down using an internal clock oscillator. The FPGA automatically powers up once the

temperature has fallen below the user-programmable lower limit (see

). The System Monitor OT signal can also be reset by writing a logic 1 to the OT bit

in System Monitor Configuration Register 1 via the JTAG DRP interface. On-chip sensors

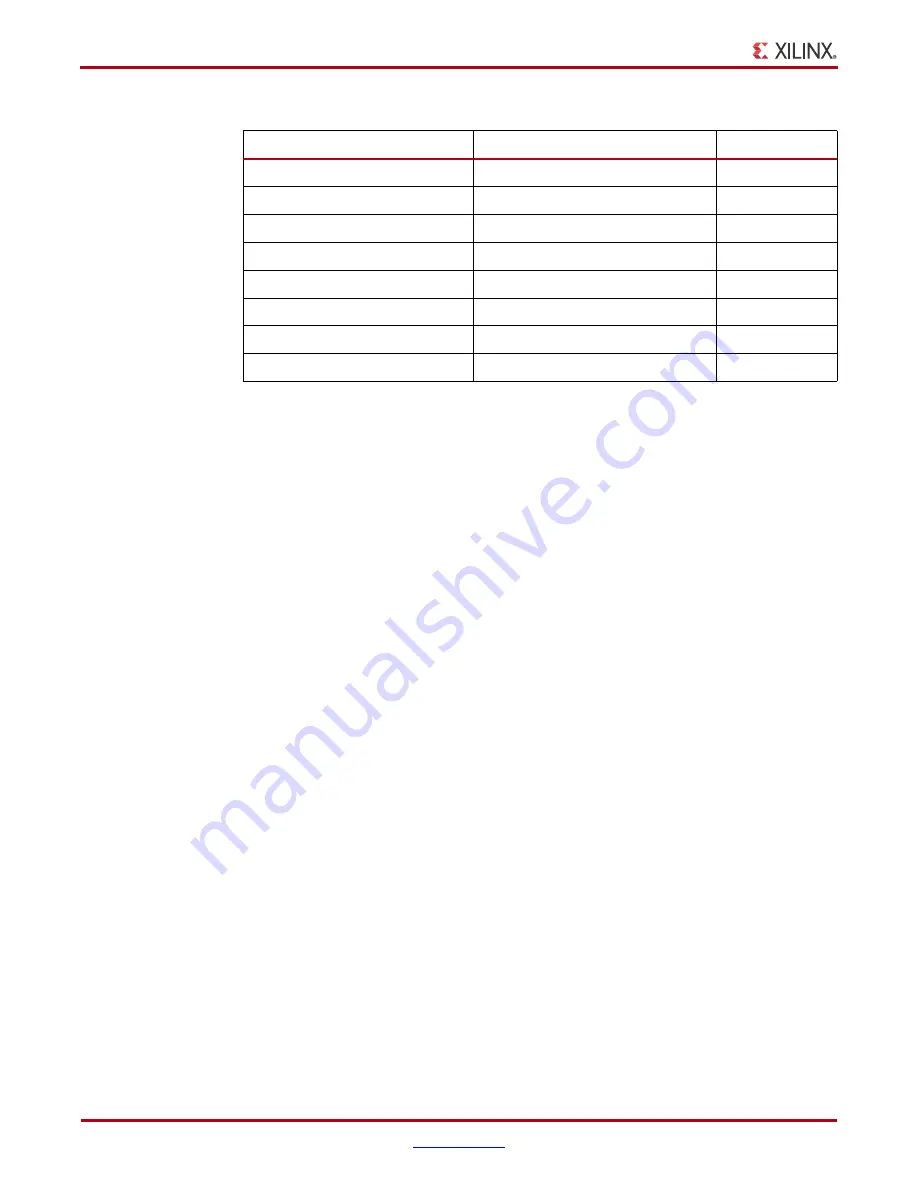

Table 17:

Alarm Threshold Registers (

50h

to

57h

)

Control Register

Description

Alarm

50h

Temperature Upper

ALM[0]

51h

V

CCINT

Upper

ALM[1]

52h

V

CCAUX

Upper

ALM[2]

53h

OT Upper

OT

54h

Temperature Lower

ALM[0]

55h

V

CCINT

Lower

ALM[1]

56h

V

CCAUX

Lower

ALM[2]

57h

OT Lower

OT

www.BDTIC.com/XILINX