Virtex-6 FPGA System Monitor

33

UG370 (v1.1) June 14, 2010

System Monitor Timing

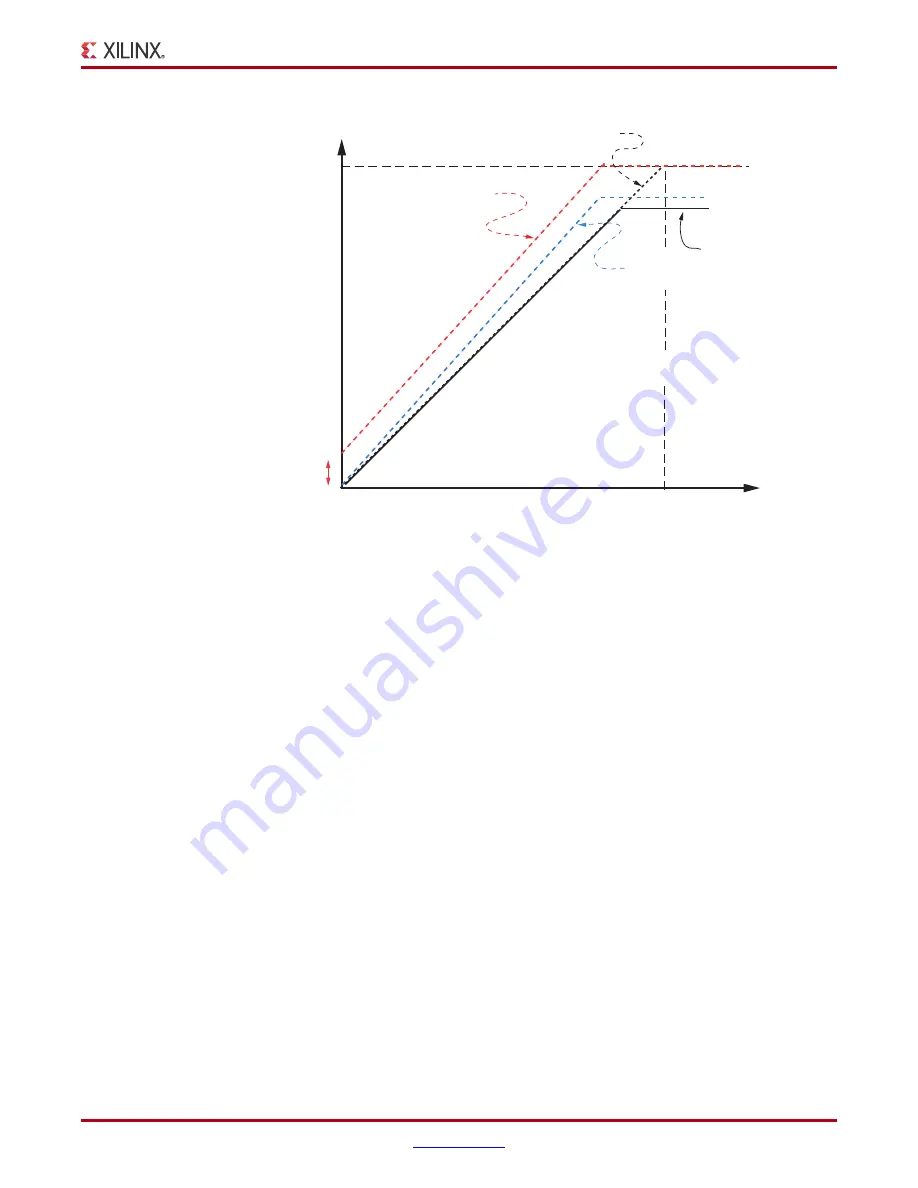

The remaining error (deviation from the dashed black line) is caused by gain error or

incorrect slope (m). This error is corrected by multiplying the ADC output code by a

correction factor.

Note:

Digital calibration can result in some loss of the analog input range at the start and end of the

ADC input range. This is illustrated in

where the ADC output never reaches 3FFh. Typically,

the loss of input range is no more than 20 mV at either end of the transfer function. For most

monitoring applications, the loss is insignificant.

System Monitor Timing

All System Monitor timing is synchronized to the DCLK. The ADCCLK is equal to DCLK

divided by the user selection in configuration register 2 (see

). The

ADCCLK is an internal clock used by the ADC and is

not

available externally. ADCCLK is

only included here to aid in describing the timing.

The ADC block in System Monitor is operated in one of two possible timing modes,

continuous-sampling mode and event-driven sampling mode.

•

In continuous-sampling mode, the ADC automatically starts a new conversion at the

end of a current conversion cycle.

•

In event-sampling mode, the user must initiate the next conversion after the current

conversion cycle ends, by using the CONVST or CONVSTCLK inputs.

The operating mode is selected by writing to configuration registers 0 (see

). A detailed timing diagram for System Monitor is shown

in

describes the timing parameters. Reference the

Virtex-6 FPGA Data Sheet

for the latest System Monitor timing specifications. The robust

nature of the System Monitor ensures continued and correct operation even if the external

clock input DCLK is stopped. In this situation, the System Monitor automatically switches

X-Ref Target - Figure 13

Figure 13:

Offset and Gain Correction

Ideal ADC

Offset and

Gain Removed

Offset

Error

Actual

Po

sitiv

e Gain Error

Offset

Removed

ADC Code

Input Voltage (V

IN

)

Code = (Gain x V

IN

) + Offset

y = m.x + c

3FFh

1V

UG370_13_060809

www.BDTIC.com/XILINX