Series AVME9125 VMEbus 6U Analog Input Board

___________________________________________________________________________________________

- 9 -

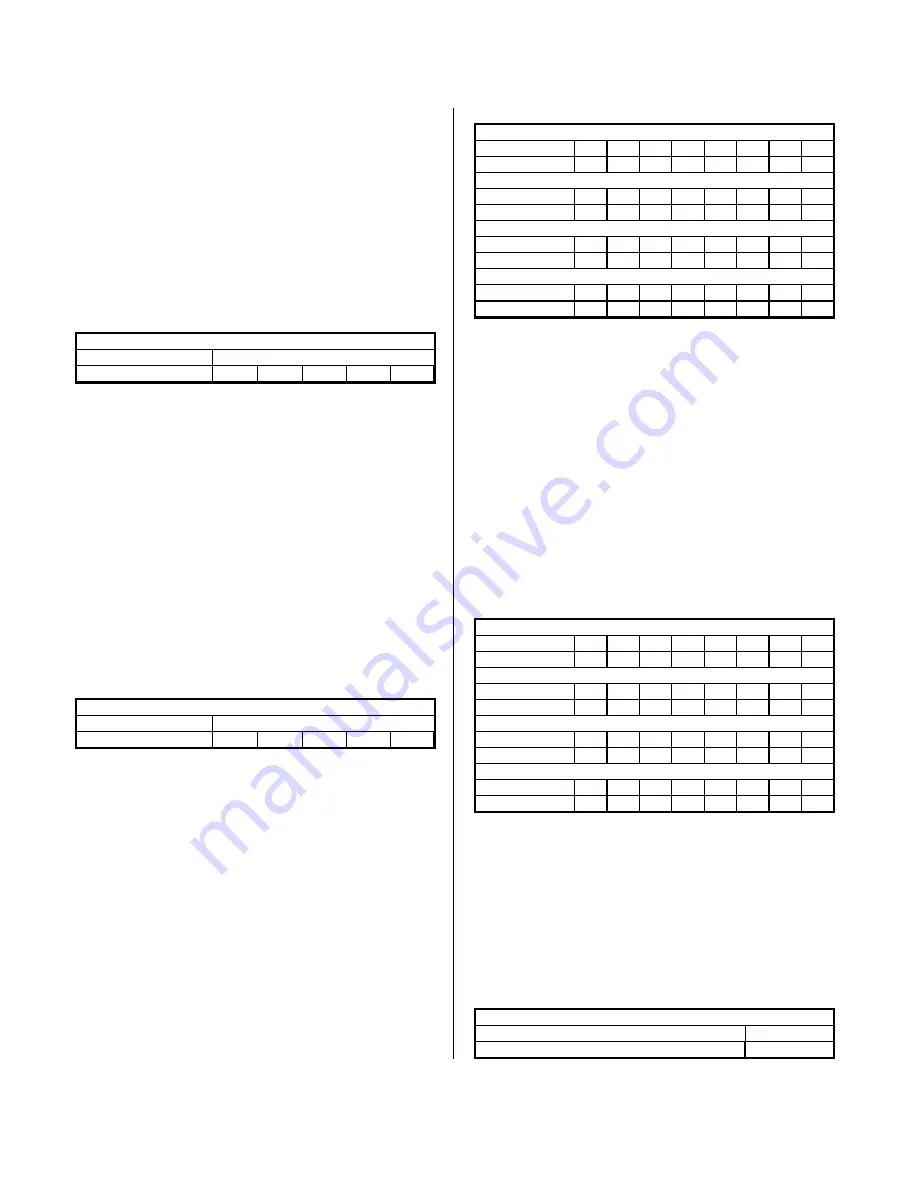

Start Channel Value Register (Read/Write, 49H)

The Start Channel Value register can be written with a 5-bit

value to select the first channel that is to be converted once

conversions have been triggered. All channels including and

between the start and end channel values are converted. A single

channel can be selected by writing the desired channel value in

both the Start and End Channel Value registers.

The Start Channel Value register can be read or written with 8-

bit data transfers. In addition, the Start Channel Value register

can be simultaneously accessed with the End Channel Value via a

16-bit data transfer. The unused bits are zero when read. The

register contents are cleared upon reset.

Start Channel Value Register

Unused

Start Channel Value

07 06 05

04

03

02

01

00

After a data conversion cycle, the internal hardware pointers

are reinitialized to the start channel value. Thus, when

conversions are started again, the first channel converted is

defined by the Start Channel Value register.

End Channel Value Register (Read/Write, 48H)

The End Channel Value register can be written with a 5-bit

value to indicate the last channel in a sequence to be converted.

When scanning, all channels between and including the start and

end channels are converted. A single channel can be selected by

writing the desired channel value in both the Start and End

Channel Value registers.

The End Channel Value register can be read or written with 8-

bit data transfers. In addition, the End Channel Value register can

be simultaneously accessed with the Start Channel Value with a

16-bit data transfer. The unused data bits are zero when read.

The register contents are cleared upon reset.

End Channel Value Register

Unused

End Channel Value

15 14 13

12

11

10

09

08

New Data Registers (Read Only, 4AH to 4DH)

The New Data registers can be read to determine which

channels of the Mail Box buffer contain new converted data. A set

bit in the New Data register indicates that the Mail Box buffer,

corresponding to the channel of the set bit, contains new

converted data. A set New Data register bit is cleared upon a read

of its corresponding Mail Box buffer.

The New Data bits are also cleared at the start of all new data

acquisition cycles initiated with the Software Start Convert

command. This is done to avoid mistaking data from an old scan

cycle with that of a new scan cycle.

The New Data registers can be read via 16-bit or 8-bit data

transfers. In addition, the register contents are cleared upon reset.

New Data Register (Read Only, 4BH)

Data Bit

07

06

05

04

03

02

01

00

Channel

07

06

05

04

03

02

01

00

New Data Register (Read Only 4AH)

Data Bit

15

14

13

12

11

10

09

08

Channel

15

14

13

12

11

10

09

08

New Data Register (Read Only 4DH)

Data Bit

07

06

05

04

03

02

01

00

Channel

23

22

21

20

19

18

17

16

New Data Register (Read Only 4CH)

Data Bit

15

14

13

12

11

10

09

08

Channel

31

30

29

28

27

26

25

24

Missed Data Registers (Read Only, 4EH to 51H)

The Missed Data registers can be read to determine if a

channel’s Mail Box buffer has been overwritten with new converted

data before the last converted value was read. A set bit in the

Missed Data register indicates a converted value corresponding to

the channel of the set bit was overwritten before being read. A set

Missed Data register bit is cleared upon a read of its

corresponding Mail Box buffer.

The Missed Data bits are also cleared at the start of all new

data acquisition cycles initiated with the Software Start Convert

command. This is done to avoid mistaking missed data from an

old scan cycle with that of a new scan cycle.

The Missed Data registers can be read via 16-bit or 8-bit data

transfers. In addition, the register contents are cleared upon reset.

Missed Data Register (Read Only, 4FH)

Data Bit

07

06

05

04

03

02

01

00

Channel

07

06

05

04

03

02

01

00

Missed Data Register (Read Only 4E)

Data Bit

15

14

13

12

11

10

09

08

Channel

15

14

13

12

11

10

09

08

Missed Data Register (Read Only 51H)

Data Bit

07

06

05

04

03

02

01

00

Channel

23

22

21

20

19

18

17

16

Missed Data Register (Read Only 50H)

Data Bit

15

14

13

12

11

10

09

08

Channel

31

30

29

28

27

26

25

24

Start Convert Register (Write Only, 52H)

The Start Convert register is a write-only register and is used

to trigger conversions by setting data bit-0 of this register to a logic

one. The desired mode of data acquisition must first be

configured by setting the following registers to the desired values

and modes: Control, Timer Prescaler, Conversion Timer, Start

Channel Value, End Channel Value, and Interrupt Vector.

This register can be written with either a 16-bit or 8-bit data

value. Data bit-0 must be a logic one to initiate data conversions.

Start Convert Register

Not Used

Start Convert

D15 to D01

D00

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com