Series AVME9125 VMEbus 6U Analog Input Board

___________________________________________________________________________________________

- 8 -

The function of each of the control register bits are described

in Table 3.3. The control register can be read or written with either

8-bit or 16-bit data transfers. A power-up or system reset sets all

control register bits to zero.

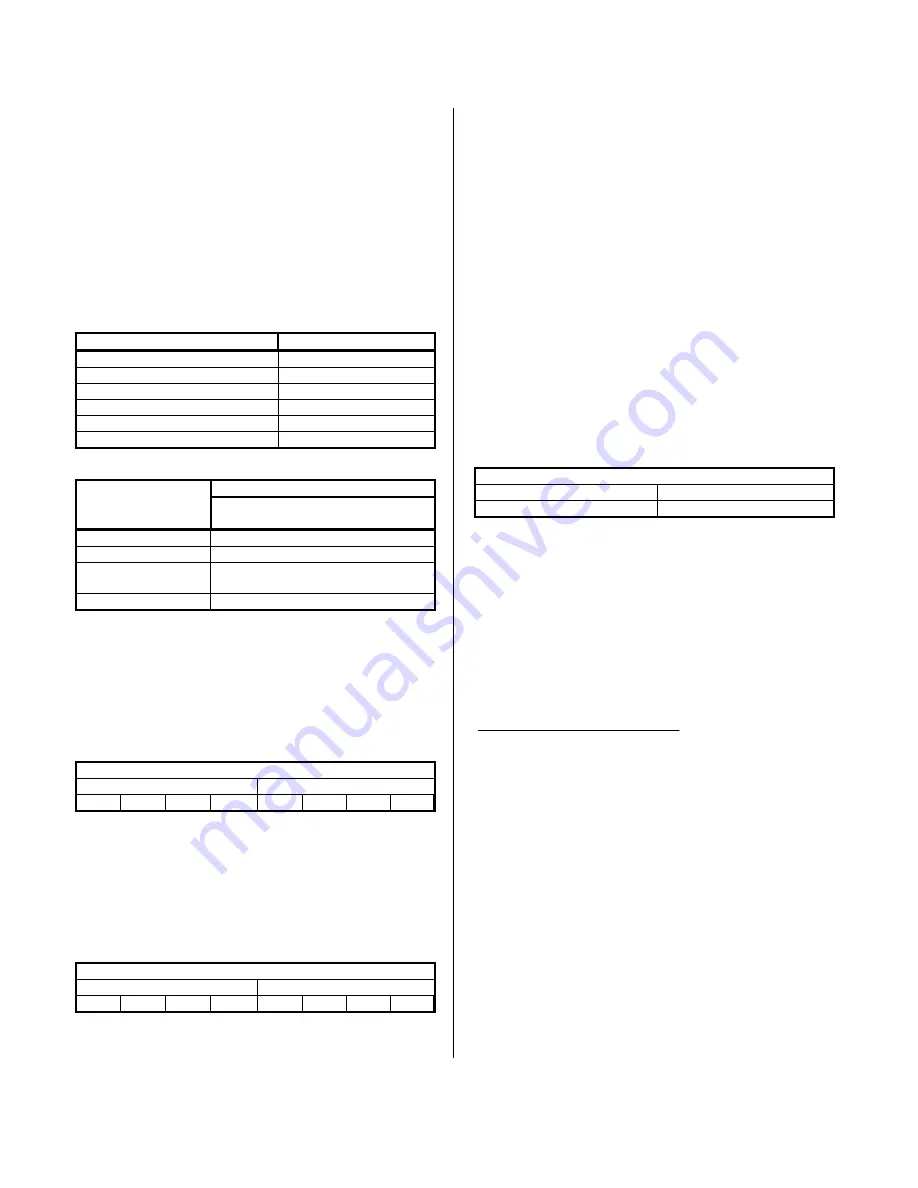

Analog Input Range and Corresponding Digital Output Code

The ideal input voltage corresponding to the

±

10 volt input

range is given in Table 3.4. In Table 3.5 the digital output code

corresponding to each of the ideal analog input values is given.

The hex codes for the converted digital output values are returned

in binary two’s complement format.

Table 3.4: Supported Full-Scale Ranges and Ideal Analog

Input

DESCRIPTION

ANALOG INPUT

Input Range

±

10V

LSB (Least Significant Bit) Weight

305

µ

V

+ Full Scale Minus One LSB

9.999695Volts

Midscale

0V

One LSB Below Midscale

-305

µ

V

- Full Scale

-10V

Table 3.5: Digital Output Codes and Input Voltages

DIGITAL OUTPUT

Binary 2’s Comp

DESCRIPTION

(Hex Code)

+ Full Scale - 1 LSB

7FFF

Midscale

0000

1 LSB Below

Midscale

FFFF

- Full Scale

8000

Interrupt Vector Register (Read/Write, 45H)

The Vector Register can be written with an 8-bit interrupt

vector. This vector is provided to the system bus upon an active

interrupt acknowledge cycle. Read or writing to this register is

possible via 16-bit or 8-bit data transfers. 16-bit data transfers will

implement simultaneous access of the Interrupt Vector and Timer

Prescaler registers. The register contents are cleared upon reset.

Interrupt Vector Register

MSB

LSB

07

06

05

04

03

02

01

00

Interrupts are released on an interrupt acknowledge cycle.

Reading of the interrupt vector during an interrupt acknowledge

cycle signals the board to remove its interrupt request.

Timer Prescaler Register (Read/Write, 44H)

The Timer Prescaler register can be written with an 8-bit value

to control the time interval between conversions.

Timer Prescaler Register

MSB

LSB

15

14

13

12

11

10

09

08

This 8-bit number divides an 8 MHz clock signal. The clock

signal is further divided by the number held in the Conversion

Timer Register. The resulting frequency can be used to generate

periodic triggers for precisely timed intervals between conversions.

The Timer Prescaler has a minimum allowed value

restriction of 5A hex or 90 decimal.

A Timer Prescaler value of

less then 90 (decimal) will result in an empty Mail Box Register

buffer.

Read or writing to this register is possible via 16-bit or 8-bit

data transfers. A 16-bit data transfer will implement simultaneous

access to the Interrupt Vector and Timer Prescaler registers. The

Timer Prescaler register contents are cleared upon reset.

The formula used to calculate and determine the desired

Timer Prescaler value is given in the Conversion Timer section

which follows immediately.

Conversion Timer Register (Read/Write, 46H)

The Conversion Timer Register can be written to control the

interval time between conversions. Read or writing this register is

possible with either 16-bit or 8-bit data transfers. This register’s

contents are cleared upon reset.

Conversion Timer Register

MSB

LSB

15 14 13 12 11 10 09 08

07 06 05 04 03 02 01 00

This 16-bit number is the second divisor of an 8MHz clock

signal and is used together with the Timer Prescaler Register to

derive the frequency of periodic triggers for precisely timed

intervals between conversions.

The interval time between conversions is generated by

cascading two counters. The first counter, the Timer Prescaler, is

clocked by an 8MHz clock signal. The output of this clock is input

to the second counter, the Conversion Timer, and this output is

used to generate periodic trigger pulses. The time period between

trigger pulses is described by the following equation:

Timer Prescaler Conversion Timer = T in seconds

∗

8

µ

Where:

T

= time period between trigger pulses in microseconds.

Timer Prescaler

can be any value between 90 and 255

decimal.

Conversion Timer

can be any value between 1 and

65,535 decimal.

The maximum period of time which can be programmed to

occur between conversions is (255

∗

65,535)

÷

8 = 2.0889

seconds. The minimum time interval that can be programmed to

occur is 11.25

µ

seconds which can be implemented as (90

∗

1)

÷

8. Any combination of the Timer Prescaler and Conversion Timer

are allowed as long as the Timer Prescaler value used is not

programmed to a value below 90 decimal.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com