Signal

Direction

Description

hip_reconfig_

writedata[15:0]

Input

16

-

bit write model.

hip_reconfig_byte_

en[1:0]

Input

Byte enables, currently unused.

ser_shift_load

Input

You must toggle this signal once after changing to user mode

before the first access to read

-

only registers. This signal should

remain asserted for a minimum of 324 ns after switching to user

mode.

interface_sel

Input

A selector which must be asserted when performing dynamic

reconfiguration. Drive this signal low 4 clock cycles after the

release of

ser_shif

t_load

.

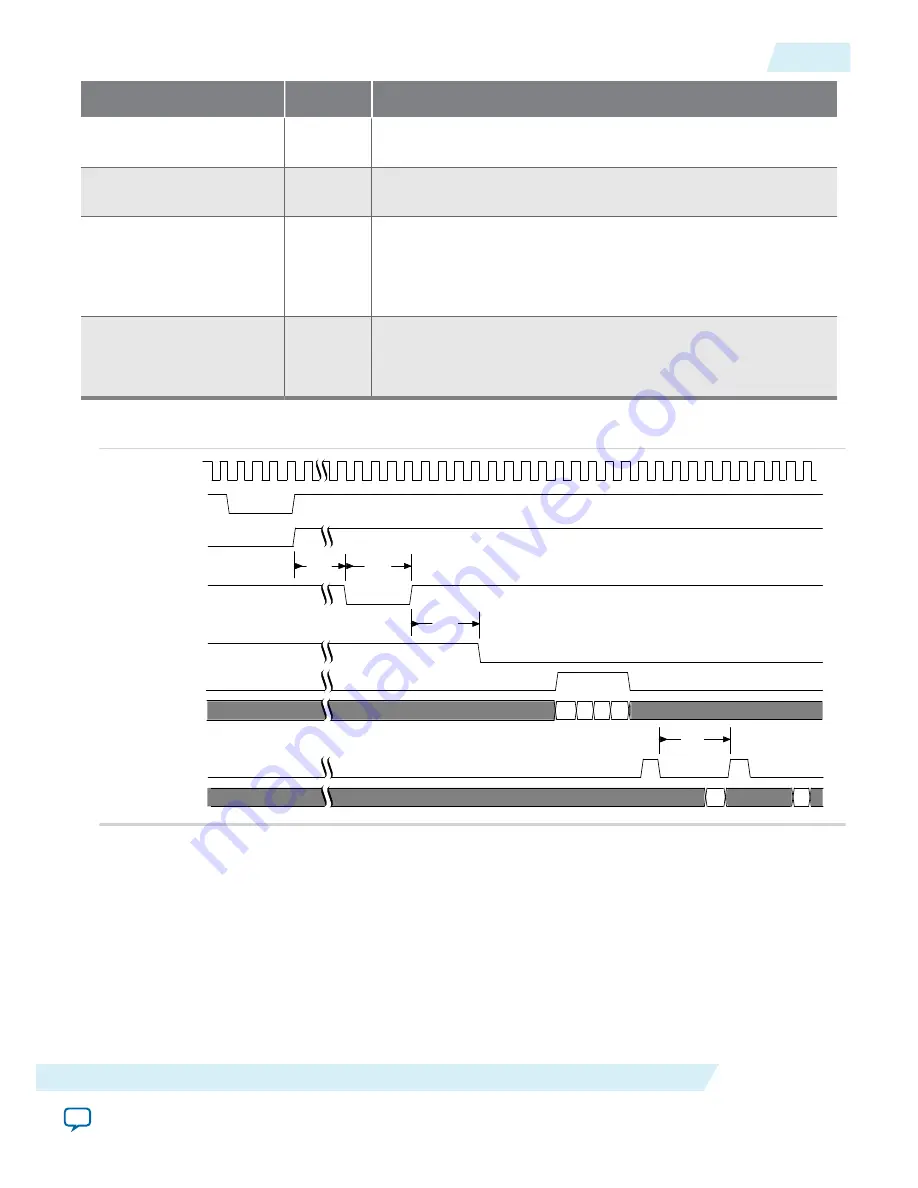

Figure 6-8: Hard IP Reconfiguration Bus Timing of Read-Only Registers

avmm_clk

hip_reconfig_rst_n

user_mode

ser_shift_load

interface_sel

avmm_wr

avmm_wrdata[15:0]

avmm_rd

avmm_rdata[15:0]

D0

D0

D1

D1

D2 D3

324 ns

4 clks

4 clks

4 clks

For a detailed description of the Avalon-MM protocol, refer to the

Avalon Memory

Mapped Interfaces

chapter in the

Avalon Interface Specifications

.

Related Information

Avalon Interface Specifications

UG-01145_avmm_dma

2015.11.02

Hard IP Reconfiguration Interface

6-21

IP Core Interfaces

Altera Corporation

Send Feedback