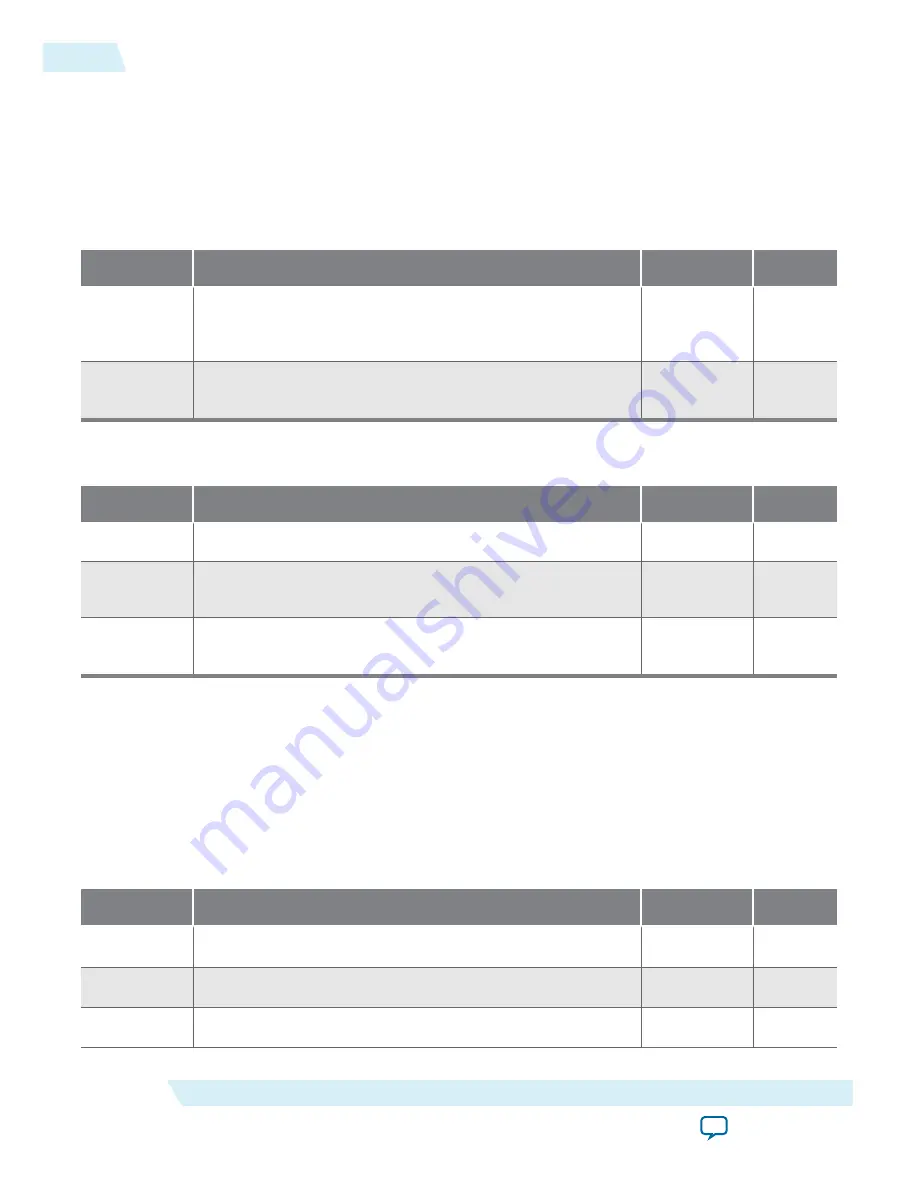

Table 7-9: CvP Data Registers

The following table defines the

CvP Data

registers. For 64-bit data, the optional

CvP Data2

stores the upper 32

bits of data. Programming software should write the configuration data to these registers. If you Every write to

these register sets the data output to the FPGA control block and generates

<n>

clock cycles to the FPGA control

block as specified by the

CVP_NUM_CLKS

field in the

CvP Mode

Control

register. Software must ensure that all bytes

in the memory write dword are enabled. You can access this register using configuration writes, alternatively,

when in CvP mode, these registers can also be written by a memory write to any address defined by a memory

space BAR for this device. Using memory writes should allow for higher throughput than configuration writes.

Bits

Register Description

Reset Value

Access

[31:0]

Upper 32 bits of configuration data to be transferred to the FPGA

control block to configure the device. You can choose 32- or 64-

bit data.

0x00000000

RW

[31:0]

Lower 32 bits of configuration data to be transferred to the FPGA

control block to configure the device.

0x00000000

RW

Table 7-10: CvP Programming Control Register

This register is written by the programming software to control CvP programming.

Bits

Register Description

Reset Value

Access

[31:2]

Reserved.

0x0000

RO

[1]

START_XFER

. Sets the CvP output to the FPGA control block

indicating the start of a transfer.

1’b0

RW

[0]

CVP_CONFIG

. When asserted, instructs that the FPGA control

block begin a transfer via CvP.

1’b0

RW

Uncorrectable Internal Error Mask Register

Table 7-11: Uncorrectable Internal Error Mask Register

The

Uncorrectable Internal Error Mask

register controls which errors are forwarded as internal

uncorrectable errors. With the exception of the configuration error detected in CvP mode, all of the errors are

severe and may place the device or PCIe link in an inconsistent state. The configuration error detected in CvP

mode may be correctable depending on the design of the programming software. The access code

RWS

stands for

Read Write Sticky meaning the value is retained after a soft reset of the IP core.

Bits

Register Description

Reset Value

Access

[31:12]

Reserved.

1b’0

RO

[11]

Mask for RX buffer posted and completion overflow error.

1b’1

RWS

[10]

Reserved

1b’0

RO

7-12

Uncorrectable Internal Error Mask Register

UG-01145_avmm_dma

2015.11.02

Altera Corporation

Registers

Send Feedback